University of Arkansas, Fayetteville ScholarWorks@UARK

Graduate Theses and Dissertations

12-2020

# Design, Fabrication, and Reliability Effects of Additively Manufactured First Level Compliant Interconnects for Microelectronics Application

Tumininu David Olatunji University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Applied Mechanics Commons, Electrical and Electronics Commons, Electronic Devices and Semiconductor Manufacturing Commons, Manufacturing Commons, and the Semiconductor and Optical Materials Commons

#### Citation

Olatunji, T. D. (2020). Design, Fabrication, and Reliability Effects of Additively Manufactured First Level Compliant Interconnects for Microelectronics Application. *Graduate Theses and Dissertations* Retrieved from https://scholarworks.uark.edu/etd/3942

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu.

### Design, Fabrication, and Reliability Effects of Additively Manufactured First Level Compliant Interconnects for Microelectronics Application

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Mechanical Engineering

by

Tumininu David Olatunji University of Port Harcourt Bachelor of Engineering in Mechanical Engineering, 2017

> December 2020 University of Arkansas

This thesis is approved for recommendation to the Graduate Council.

David Huitink Ph.D., Thesis director

Wenchao Zhuo Ph.D., Committee member

Yarui Peng Ph.D., Committee member

#### ABSTRACT

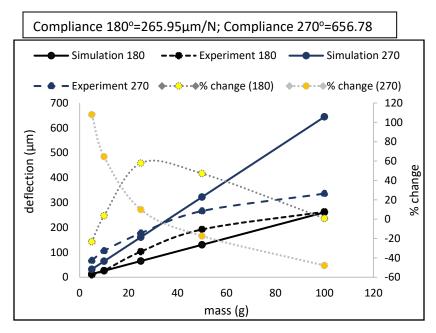

Semiconductor packaging and development is greatly dependent on the magnitude of interconnect and on-chip stress that ultimately limits the reliability of electronic components. Thermomechanical related strains occur because of the coefficient of thermal expansion mismatch from different conjoined materials being assembled to manufacture a device. To curb the effect of thermal expansion mismatch between conjoined parts, studies have been done in integrating compliant structures between dies, solder balls, and substrates. Initial studies have enabled the design and manufacturing of these structures using a photolithography approach which involves a high number of fabrication steps depending on the complexity of the structures and the masked approach may cause some structural alignment concerns during manufacturing. This research involves the fabrication of these structures using a different novel approach, utilizing additive manufacturing that reduces the number of fabrication steps required to obtain compliant geometries, eliminating the requirement for alignment tools, while also providing a platform for unique compliant structures. Additive manufacturing offers a solution to increasing fabrication concerns for electronics and additive manufacturing has emerged as a potential technology for improved customized and complex part fabrication. This thesis provides a review of common additive manufacturing approaches ranging from material development, process fabrication development, and applications that have been demonstrated in the electronics industry whilst also eliminating non critical process such as masking concerns, depending on geometry size. This thesis discusses two main methods of fabrication and analyzes the properties and effects of these interconnect structures on a die. Structural finite element thermal cycling simulations between -40 to 125°C show about a 115% increase in the solder joint fatigue life. Additionally, fabricated test structures created directly on a PCB were experimentally characterized for compliance using a micro-indenter tester, showing a mechanical compliance

range of 265.95 to 656.78 µm/N for selected design parameters to be integrated into a test vehicle. This approach can accomplish similar thermomechanical stress alleviation to formerly reported methods, but with fewer process steps, and potential for new geometry manufacturing. Further validation of the finite element reliability has been done by integrating an in situ elevated temperature shear stress study. The compliant interconnect packaged device demonstrated enhanced electrical reliability performance when compared with the package without the interconnects.

#### ACKNOWLEDGEMENT

Firstly, I would like to express my sincere gratitude to my academic advisor, Dr. David Huitink, for his mentorship, professional advisory, knowledge, support, and motivation throughout my research and for helping me discover new skills within myself. I would like to thank Dr. Peng and Dr. Milkovjic for their additional contribution and advisory in my research. I would like to thank Mr. Errol Potter and Mrs. Kaoru Potter for their help in the usage of HiDec state of the art facility. I would also like to extend my thanks to my thesis committee member, Dr. Zhou.

I would like to thank every member of the POETS group and the University of Arkansas Power group current and past whose previous research effort has allowed me to prepare and take the necessary steps in my research. My sincere thanks to Mahsa Montazeri who has provided initial onboarding assistance in simulation and computational analysis.

Additionally, I would like to thank the Empire lab and faculty members at the Mechanical Engineering Department for their overall direct and indirect support through my master's degree time at the University of Arkansas.

## DEDICATION

I dedicate this thesis to my parents, Mr., and Mrs. Olatunji for their endless, love, support that has helped me through this phase of my career.

# TABLE OF CONTENTS

| CHAPTER 1: | INTRODUCTION                                             | 1   |

|------------|----------------------------------------------------------|-----|

|            | 1.1: Background                                          | 1   |

|            | 1.2: Research Objectives                                 | 4   |

|            | 1.3: Organization of thesis                              | 6   |

| CHAPTER 2: | LITERATURE REVIEW                                        | 8   |

|            | 2.1: Additive Manufacturing in Electronics               | 8   |

|            | 2.2: Electronics packaging for power module devices      | 13  |

|            | 2.3: Examples of Mechanical Enhanced Compliant Structure | 15  |

|            | 2.4: Working principle of Compliant Interconnects        | 18  |

| CHAPTER 3: | DESIGN FABRICATION APPROACH AND METHODOLOGY              | 20  |

|            | 3.1: Design Variables                                    | 20  |

|            | 3.1.2: Copper Post Variables                             | 21  |

|            | 3.2: Method of Fabrication                               | .22 |

|            | 3.2.1: 3D printing technique selection                   | .23 |

|            | 3.2.2: Material selection                                | .24 |

|            | 3.2.3: ABS method of fabrication overview                | .27 |

|            | 3.2.4: BVOH method of fabrication overview               | .31 |

|            | 3.3: Process Refinement.                                 | .33 |

|            | 3.4: Assembly                                            | .35 |

|            | 3.5: Process and material characterization               | .38 |

|            | 3.5.1: BVOH characterization                             | .38 |

|            | 3.5.1.1: BVOH mold negative path degradation             | .41 |

|            | 3.5.2: ABS characterization                              | .41 |

|            | INTERCONNECTS MODELING AND CHARACTERIZATION (Modeling a  |     |

|            | 4.1: Material modeling                                   | .43 |

|            | 4.1.1: Solder                                            | .43 |

| 4.1.2: Copper45                                                                                  |

|--------------------------------------------------------------------------------------------------|

| 4.1.3: FR445                                                                                     |

| 4.2: Mechanical Compliance46                                                                     |

| 4.2.1: Mechanical Stiffness and Compliance study46                                               |

| 4.2.2: Mechanical characterization and study47                                                   |

| 4.2.2.1: Experimental effect of subtended angle (α) on mechanical stiffness and compliance       |

| 4.2.2.2: Effect of beam width (w) on mechanical stiffness and compliance                         |

| 4.2.2.3: Effect of beam thickness (t) on mechanical stiffness and compliance                     |

| 4.2.2.4: Effect of beam length (L) from center radius (R) on mechanical stiffness and compliance |

| 4.3: Interconnect thermomechanical fatigue life                                                  |

| 4.3.1: Copper compliant interconnect fatigue life                                                |

| 4.3.2: Solder joints thermo-mechanical fatigue life                                              |

| 4.4: Electrical characterization60                                                               |

| CHAPTER 5: EXPERIMENTAL CHARACTERIZATION AND VALIDATION61                                        |

| 5.1: Compliance experimental testing61                                                           |

| 5.2: Experimental testing comparison with simulation61                                           |

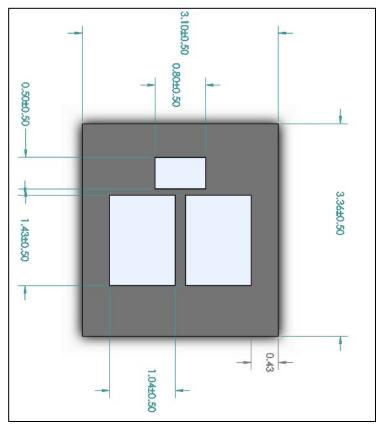

| 5.3: Design strategy for assembly on test vehicle                                                |

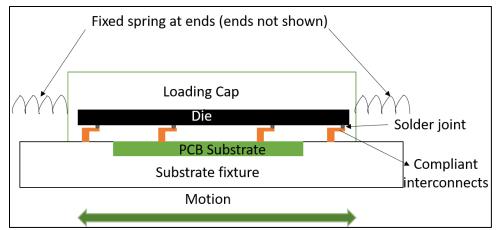

| 5.4: Reliability prediction via experimental testing64                                           |

| 5.4.1: Preliminary Mechanical cycling effect on resistance                                       |

| CHAPTER 6: CONCLUSIONS AND FUTURE WORK                                                           |

| 6.1: Conclusion                                                                                  |

| 6.1.1: Major research findings73                                                                 |

| 6.2: Future Work                                                                                 |

| REFERENCES                                                                                       |

| APPENDIX:                                                                                        |

| APPENDIX A: Mechanical Compliance testing procedure82                                            |

| APPENDIX B: Interconnect PCB design for in situ reliability resistance testing | 85 |

|--------------------------------------------------------------------------------|----|

| APPENDIX C: Test vehicle wafer fabrication                                     | 86 |

| APPENDIX D: Tribometer in situ resistance test procedure                       | 89 |

| APPENDIX E: Fixture dimensions and machining                                   | 91 |

# LIST OF TABLES

| Table 2-1: 3D printing techniques and application in electronics fabrication                                                             | 12 |

|------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 3-1: Comparison of common 3D printing materials                                                                                    | 24 |

| Table 3-2: SAC 305 solder ball reflow temperature profile                                                                                | 37 |

| Table 4-1: Anand's parameters for Pb37Sn63                                                                                               | 44 |

| Table 4-2: Strain hardening parameters for nonlinear copper alloy                                                                        | 45 |

| Table 4-3: Solder ball cycles to failure comparison of a package with compliant interconnectsand package without complaint interconnects |    |

| Table 4-4: Electrical inductance comparison of common interconnects methods and complia   interconnects                                  |    |

## LIST OF FIGURES

| Figure 1-1: Gordon Moore's transistor predictor chart                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2: Figure 1-2: Wire bond assembled package4                                                                                |

| Figure 1-3: flip-chip bonded assembled package5                                                                                     |

| Figure 2-1: Inkjet printing and deposition technique on a substrate9                                                                |

| Figure 2-2: Aerosol printing and deposition technique10                                                                             |

| Figure 2-3: Metalized polymer spheres15                                                                                             |

| Figure 2-4: SEM images of copper bumps16                                                                                            |

| Figure 2-5: SEM images of copper nanowires17                                                                                        |

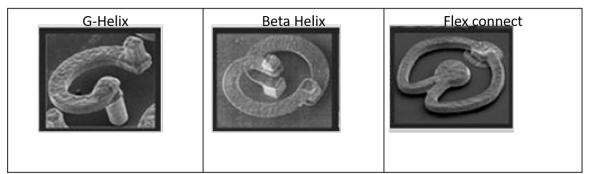

| Figure 2-6: SEM images of different compliant interconnect geometries17                                                             |

| Figure 3-1: Additive manufactured interconnect model                                                                                |

| Figure 3-2: Image of a porous plot for thin molds22                                                                                 |

| Figure 3-3: Process flow for additive manufacturing of compliant interconnects                                                      |

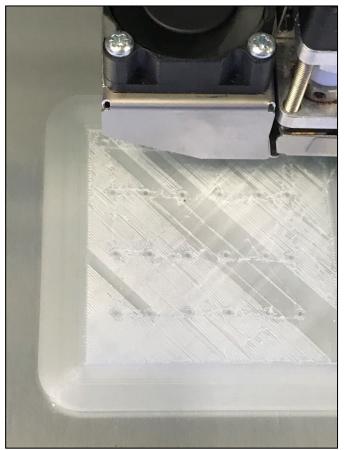

| Figure 3-4: Pictorial image of 3D FDM printer printing on a PCB27                                                                   |

| Figure 3-5: Electrical electrodeposition set up                                                                                     |

| Figure 3-6: Electrodeposited copper post                                                                                            |

| Figure 3-7: (a) stencil image after the printing of horizontal seed copper layer (b) Image of applied conductive paint              |

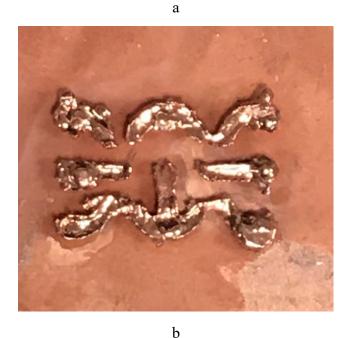

| Figure 3-8: (a) Image of fabricated compliant interconnects within the mold (b) Image of compliant interconnects after mold removal |

| Figure 3-9: (a) BVOH print without cellulose coat (b) BVOH print with cellulose coat32                                              |

| Figure 3-10: Power polishing tool                                                                                                   |

| Figure 3-11: Printed negative photomask on a fabricated sample                                                                      |

| Figure 3-12: Exposed dry film on a fabricated sample35                                                                              |

| Figure 3-13: Optical images of interconnects (a) before polishing (b) after polishing35                                             |

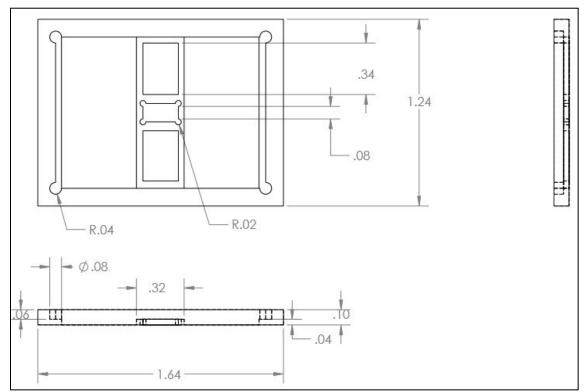

| Figure 3-14: Die assembly mechanical fixture design                                                                                 |

| Figure 3-15: Solder mask opening on interconnect                                                                                    |

| Figure 3-16: An assembled device for testing                                                                                        |

| Figure 3-17: Weight measuring apparatus                                                                                             |

| Figure 3-18: BVOH etch rate and reaction in acetone                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-19: BVOH copper sulphate absorption rate without cellulose coating                                                                 |

| Figure 3-20: Partially coated BVOH absorption rate                                                                                          |

| Figure 3-21: Visible degradation during electrodeposition of BVOH (a) Without coating (b) With coating                                      |

| Figure 3-22: ABS reaction in copper sulphate solution                                                                                       |

| Figure 3-23: ABS etch rate in acetone                                                                                                       |

| Figure 4-1: (a) Modeled shape of PCB (b) Actual shape of PCB highlighting internal components                                               |

| Figure 4-2: Directional application of force for lateral and vertical compliance measurements                                               |

| Figure 4-3: Effect of subtended angle (α) on mechanical stiffness and compliance of the beam                                                |

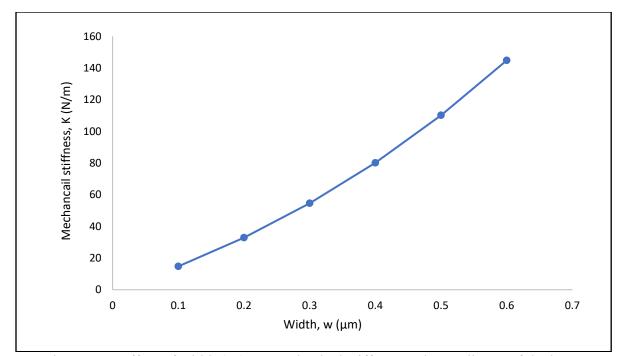

| Figure 4-4: Effect of width (W) on mechanical stiffness and compliance of the beam50                                                        |

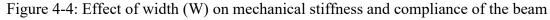

| Figure 4-5: Effect of the center radius (R) on mechanical stiffness and compliance of the beam51                                            |

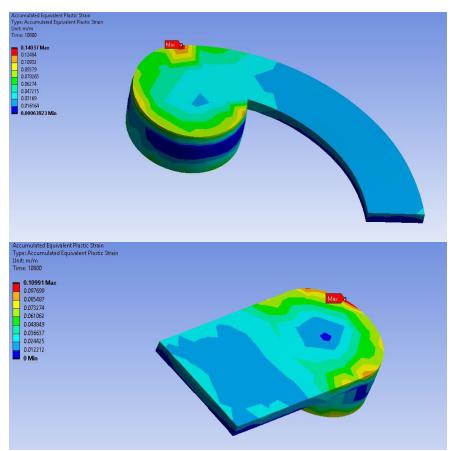

| Figure 4-6: Maximum accumulated plastic strain for curved and straight beams                                                                |

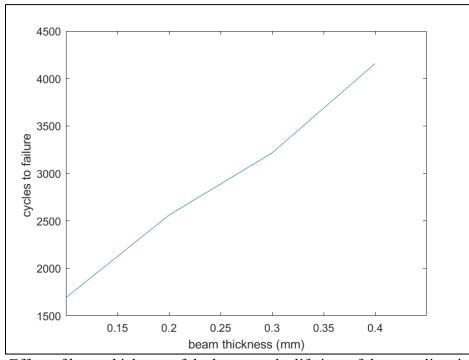

| Figure 4-7: Effect of beam thickness of the beam on the lifetime of the compliant interconnects                                             |

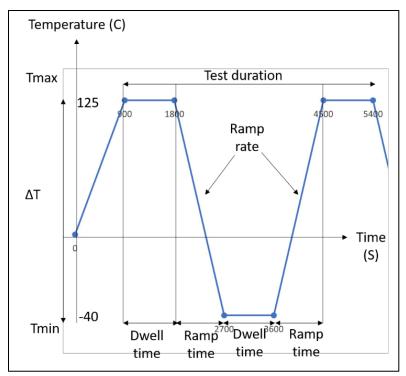

| Figure 4-8: Schematic of thermal cycling profile for modeling and testing55                                                                 |

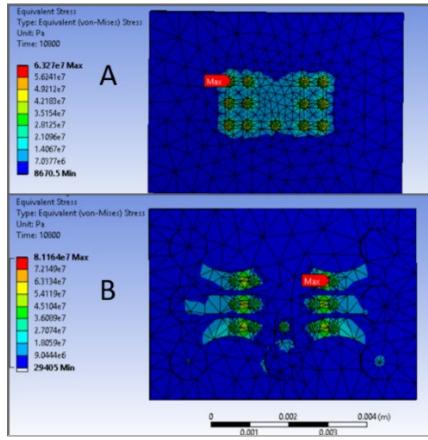

| Figure 4-9: Top view of von- Mises stress mapping and distribution for (a) without compliant interconnects (b) with compliant interconnects |

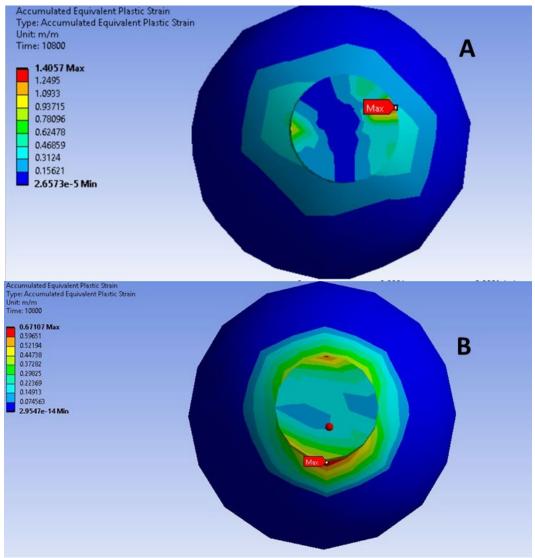

| Figure 4-10: Maximum accumulated plastic strain distribution (A) Bare solder (B) Compliant integrated solder joint                          |

| Figure 4-11: Effect of beam width on solder fatigue life                                                                                    |

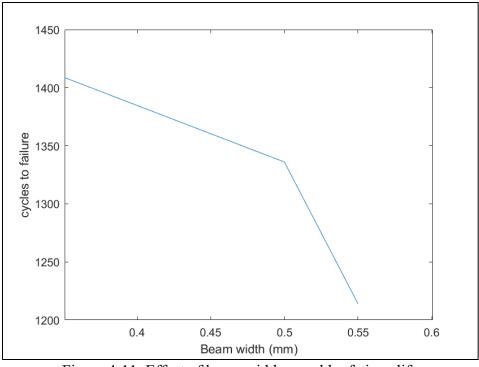

| Figure 4-12: Effect of beam thickness on solder fatigue life                                                                                |

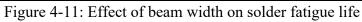

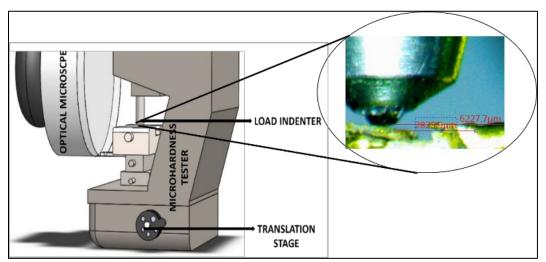

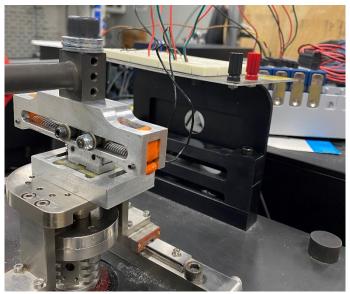

| Figure 5-1: Mechanical compliance experimental setup61                                                                                      |

| Figure 5-2: Effect of subtended angle (α) on vertical mechanical compliance (Simulation and experimental)                                   |

| Figure 5-3: Dimensional representation of CREE MOSFET test vehicles                                                                         |

| Figure 5-4: loading configuration for resistance in situ shear test                                                                         |

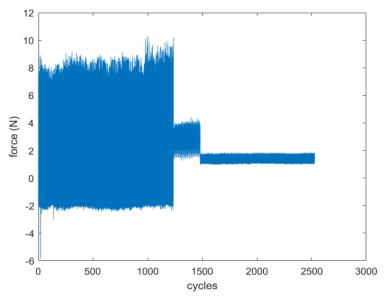

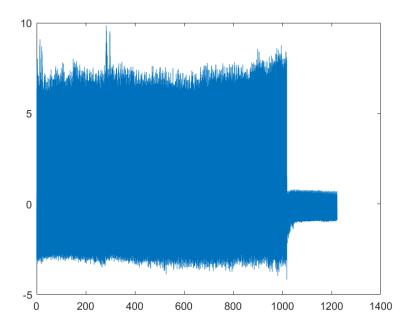

| Figure 5-5: Mechanical shear stress test apparatus                                                                                          |

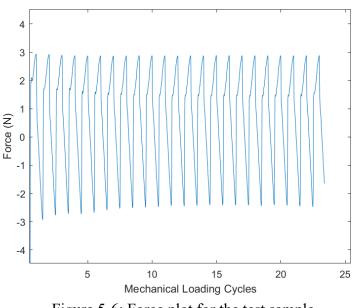

| Figure 5-6: Force plot for the test sample                                                                                                  |

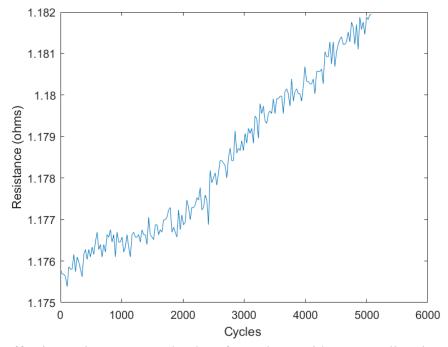

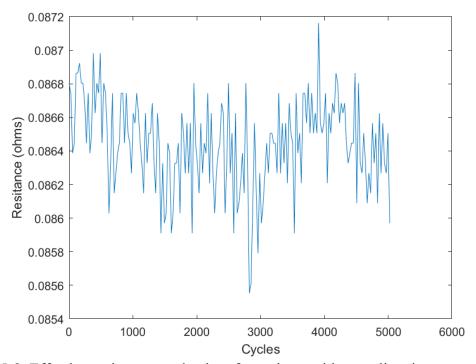

| Figure 5-7: Effective resistance to cycle plot of a package without compliant interconnects ( | <u>a</u> 50 |

|-----------------------------------------------------------------------------------------------|-------------|

| C                                                                                             | 68          |

| Figure 5-8: Effective resistance cycle plot of a package with compliant interconnects @ 50    |             |

| C                                                                                             | 69          |

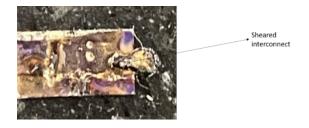

| Figure 5-9: Mechanism of failure of the compliant interconnect                                | 70          |

| Figure 5-10: Lifetime of test vehicle without compliant interconnects @ 25C                   | 70          |

| Figure 5-11: Lifetime of test vehicle with compliant interconnects @ 25C                      | 71          |

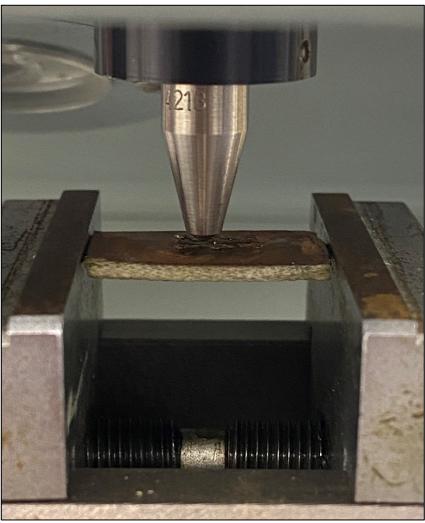

| Figure A-1: Sample positioned in clamp for beam deflection measurements                       | 82          |

| Figure A-2: Load placement area in microhardness tester                                       | 83          |

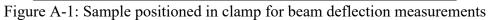

| Figure A-3: Optical imagery of beams during load application (a) unclear image (b) image.     |             |

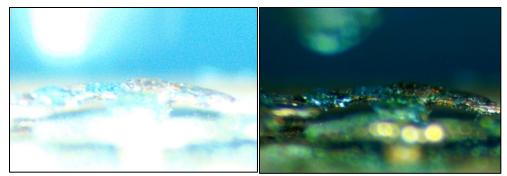

| Figure B-1: Picture of designed and fabricated PCB for in situ resistance testing             | 85          |

| Figure C-1: Image of plane 4" silicon wafer before processing                                 | 86          |

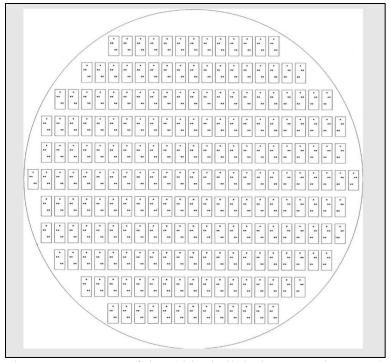

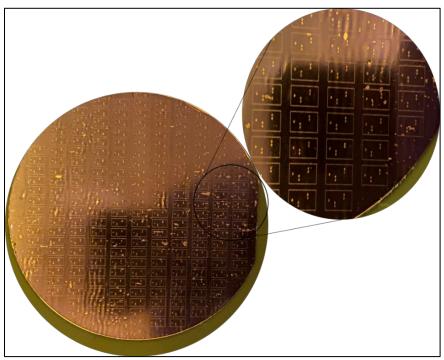

| Figure C-2: Image of the solder ball design on photomask                                      | 87          |

| Figure C-3: Image of an exposed dry film on silicon wafer                                     | 87          |

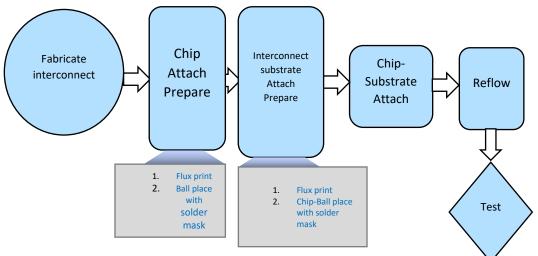

| Figure C-4: Die assembly process flow                                                         | 88          |

| Figure E-1: Plan and elevation drawings with dimensions for mechanical fixture                | 91          |

|                                                                                               |             |

#### **1. INTRODUCTION**

#### 1.1 Background

Given the rapid development and miniaturization of already existing electronic devices and components, which causes reliability challenges for conventional organic packaging approaches due to the underlying limitation of machining and fabricating micro components sizes, it is paramount for researchers to investigate more effective methods of fabrication that can meet the industrial needs for miniaturized microelectronics fabrication. In recent times, researchers have investigated integrating additive manufacturing methods in electronics fabrication. Additive manufacturing is the layer-by-layer build-up of materials to form a part or component. This method of fabrication offers an effective fabrication methods. Generally, additive manufacturing offers an easier path to fabricating microelectronics and also provides opportunities for the fabrication of unique customized designs for electronics parts and components whilst also reducing effective fabrication costs and reducing the number of process steps required to manufacture similar components in comparison to subtractive fabrication methods [1].

The overall set up, size designs, and assembly of microelectronics make it extremely difficult for conventional manufacturing approaches to be utilized in fabrication. Electronics components may consist of functional traces or interconnection structures such as compliant interconnects, conductive paths, chip substrates, etc. While conventional approaches have been enhanced through some processing techniques such as photolithography to aid in the miniaturization of the components' sizes, there are concerns with integrating multiples fabrication procedures such as difficulties in customization of designs for fabrication, increased number of process steps to

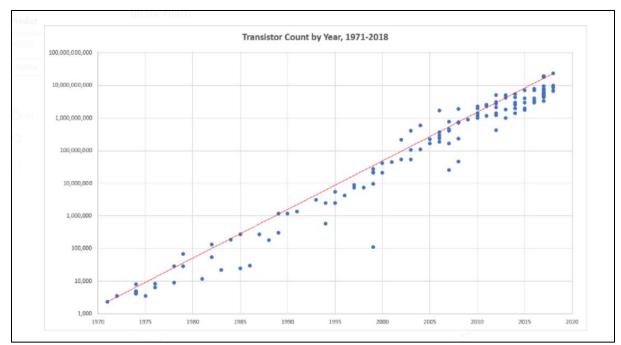

fabrication, low throughput turn out, exposure of materials to corrosive chemicals, etc. Just as predicted by Gordon Moore, the co-founder of Intel, the constant increase in the number of chips on substrates would inadvertently cause challenges in device size limitations requiring greater package integration technology approaches to aid the increasing development and power push on electronics and multi-chip integration [2].

Figure 1-1 - Gordon Moore's transistor predictor chart [3]

Customization and complex geometry creation are made possible through additive manufacturing causing a paradigm shift in research and investigation of alternate complex geometry manufacturing methods, different from conventional subtractive manufacturing processes. Additive manufacturing provides numerous advantages such as aiding the fabrication of embedded functional elements during the step by step building of components enabling the integration of conductive circuit paths for electronics applications [4]. Salaoru et al. illustrate some of the advantages of additive manufacturing in the ease of design customization, low cost of production, etc. [5]. Additive manufacturing approaches have even been leveraged in the nonelectronics industry such as in the fabrication of human tissues and organs highlighting its vast industrial applications [6], [7], etc.

With the need for advanced integration methods and growing markets in customizable electronics, additive manufacturing offers a great opportunity in microelectronic packaging integration methods.

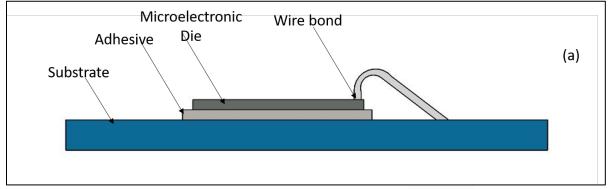

Electronic packages typically comprise multiple components that are mechanically assembled to form a singular working device and these assemblies are optimized for best mechanical and thermal performances. Electronic packages are constantly being improved for advanced performances and the increased performance expected from these devices is dependent on the reliability capabilities in geometrical designs, structural enhancement, and architectural and interconnect placements. Semiconductors are intricate components to most electronic devices and their reliability is paramount to the overall reliabilities of most power electronics. One of the major points of failure in a semiconductor device during device or system assembly and working conditions is at the interconnect level. Mechanical stresses that occur at these regions are caused by differential thermal contraction between dies, solder balls, and substrate for flip-chip devices [8]. There are many other ways of assembly a chip on a substrate such as a tape automated bonding and conventionally through wire bonds. Wire bonds have many demerits in optimizing the design space, mechanical and geometrical concerns, and even electrical disadvantages such as inherent crosstalk via parasitic inductances. Wire bonds pose concerns with thermal expansion mismatch between the substrate and the die, but most importantly the architectural design provides poorer thermal management control and consequently affects the reliability of these electronic packages as in a wire bond assembly, the heat generated region faces the die and thus prevents and/or reduces convective air cooling.

Experiments were done by Engl et al.,[9] comparing the effects of wire bonds and the flip-chip interconnect method validates the benefits and gives a better understanding of the industrial paradigm shift to the flip-chip method of assembly. They showed that with wire bonds, and increased power loss is expected, an increase in parasitic effects such as inductance is also observed when compared with solder balls-based assembly.

#### **1.2 Research Objectives**

Integration of high powered semi-conducting materials such as silicon carbide can push the working temperature of modules as high as 500 °C [10]. Beyond the general obvious reason to shift from wire bond based assembly due to its mechanical unreliability, poor thermal conductivity, and architectural design causing a large footprint, but also electrically, wire bonds negatively impact the electrical performance of integrated circuits through parasitic self-inductances.

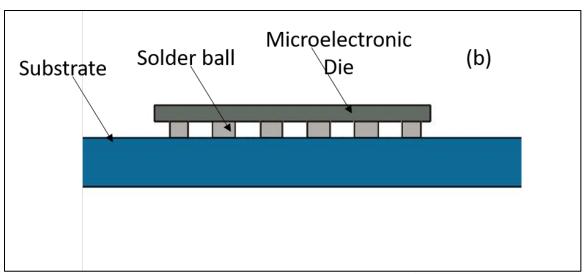

The numerous demerits of wire bonds have encouraged the integration of the flip-chip method as a first-level interconnect for die to substrate packaging that provides improved mechanical and electrical performance such as ball-grid arrays (BGAs).

Figure 1-2: Wire bond assembled package [11], [12]

Figure 1-3: flip chip bonded assembled package [11], [12]

The working temperature of high-powered integrated circuits poses a great area of concern in the mechanical reliability of the conjoined parts due to the assembly and packaging of different materials with dissimilar coefficients of thermal expansion even with the flip-chip assembly method.

To improve the overall fatigue life of power integrated devices, this research focuses on developing a novel process to enable the fabrication of mechanical compliant electrical interconnect for power module assembly and to also improve solder ball thermomechanical reliability. Typically, electronic interconnect packaging can be subdivided into three (3) categories:

- i. First level interconnect used to package an integrated circuit die to a substrate

- Second level interconnects used to package multiple integrated circuits die/chip to a systems board.

- iii. Third-level interconnect is used to package multiple systems to a unified board creating a larger system.

These interconnects perform the following functions in a power device mechanical robustness through the underfill materials and solder balls, electrical conductivity for signal, and electrical connection, and they can even help in thermal conduction of heat away from the system. This thesis also analyzes the certain properties of the manufactured device through mechanical, electrical, and reliability computational characterizations. Further experimental studies and tests are done to validate simulated results.

Some other objectives this research sought to improve includes:

- A cost-effective method of fabricating multiple compliant interconnect devices across the board by using readily available materials.

- Develop an easy to understand and use repeatable process for assembling power devices on these structures.

- Improve throughput for manufacturing of these structures by encouraging a wafer method of fabrication that can be diced afterward.

#### 1.3 – Organization of Thesis

This thesis includes five chapters, and the content of each chapter is briefly described below. <u>Chapter 2</u>: This chapter presents a comprehensive review of the existing literature of additive manufacturing applied in microelectronics fabrication. Here common additive manufacturing methods are highlighted and some examples of additive manufacturing applications into manufacturing components of electronics. Further review of structural enhancement techniques that have been integrated into chip substrate interconnects for mitigating stresses.

<u>Chapter 3</u>: The novel additive manufacturing approach of manufacturing this micro-compliant structure is presented, details in material selection and characterization are also highlighted including electroplating requirements for current and voltage. Further discussion includes

possible structural refinement of the structure and assembly methods of the dies on the compliant interconnect structure

<u>Chapter 4</u>: A complete step by step method of accurately modeling these structures for mechanical and reliability characterization is discussed with a process flow chart while also highlighting some of the boundary conditions that were applied to properly model operating conditions for testing and experiments

<u>Chapter 5</u>: Here the experimental characterization and validation process and challenges are accurately discussed. Validation and comparative study between experimental data and computational data are also presented generating an informed conclusion from both approaches. The sample is tested on a dummy MOSFET test vehicle and the experimental result is discussed. <u>Chapter 6</u>: The final chapter discusses the main research findings gotten from this research thesis, highlighting the impact on microelectronics and presents areas for further studies.

#### **2. LITERATURE REVIEW**

#### 2.1 Additive Manufacturing in Electronics

The concept of additive manufacturing is highly dependent on conjoining the matrix elements of the primary material of fabrication. Typically, the parent material is melted and fed to start the fabrication process usually at a specific feed or flow rate [13]. Many methods and printing technologies aid the fabrication of electronics components and some of the commonly used fabrication process steps for melting parent matrix materials ranging from electron beam melting, laser metal deposition, laser beam melting, and the use of a conventional heating block. However, more efficient ways to aid layer by layer fabrication should be explored and exploration of various fabrication approaches depends on the component application, some of the properties per application to be considered may consist of surface roughness concerns, size of embedded features in components, the strength of the component, and porosity effects [14]. Many additive fabrication methods exist that aid little or no change in material chemistry such as fused deposition modeling technology, inkjet printing, direct metal, and stereolithography-based printing like stereolithography apparatus, (SLA) and selective laser sintering (SLS) [5]. Additive based manufacturing technology is a step-based deposition of material to form a proposed designed structure. Here, some of the common methods of additive manufacturing incorporated for electronics application and fabrication is highlighted.

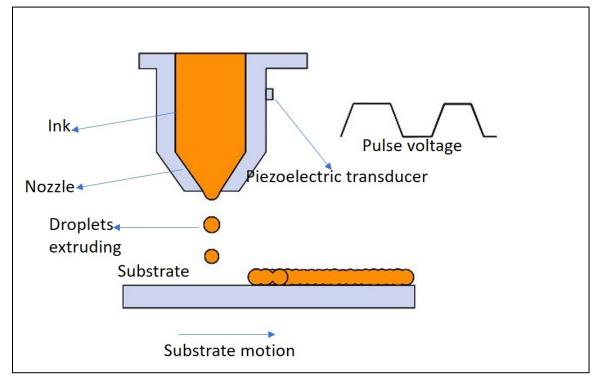

For example, inkjet printing technology is a common AM fabrication approach and offers a straightforward fabrication path for conductive paths in electronics by depositing ink droplets onto a substrate where the print head provides the driving force (thermal or piezoelectric) for accurate reliable material deposition see figure 2-1. This printing procedure can also be described as the powder bed printing method [15].

Numerous factors can affect the adoption of a printing method or selection and application of material for electronics. These factors may include but are not limited to the printability of material, extrusion pressure/temperature, dependent on the driving force, the diameter of the extruder nozzle, the viscosity of the material, the properties of the material [16]-[18]. One of the major drawbacks with using the inkjet printing technique is the limitation of the viscosity of the material that can be integrated into this additive manufacturing method, usually in the range of 20 - 40 MPa-s [19], [20]

Figure 2-1: Inkjet printing and deposition technique on a substrate

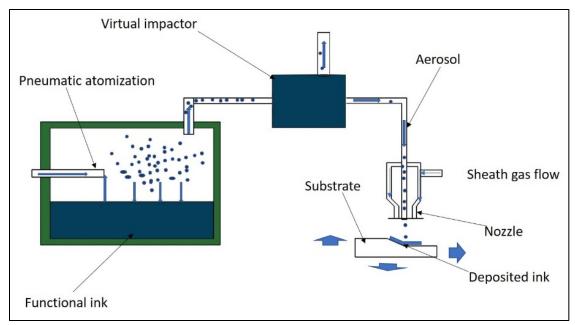

Another common AM printing technique is aerosol jet printing which mode of operation that involves changing the material from liquid to vapor based on extrusion using a high – velocity nozzle. This printing technique provides a great advantage in reducing the cure time of the dispensed material during printing because the printing material is partially dried during phase change from liquid to vapor before the deposition is illustrated in figure 2-2.

Figure 2-2: Aerosol printing and deposition technique adopted from [21]

There exist other types of 3D printing AM techniques such as stereolithography based printing method, fused deposition printing method, an extrusion-based 3D printing like syringes and pneumatic micro dispensing pump.

The stereolithography method utilizes the use of ultraviolet light to cure resins and metal powders in a systematic sequential arrangement to fabricate components and can be subdivided into Selective Laser Melting and Selective Laser Sintering. Stereolithography enables rapid prototyping and expedited testing of designs [22] and Maalderink et al. highlights various examples of integrating stereolithography-based 3D printing methods [23].

The fused deposition model or fused filament fabrication printing technology commonly abbreviated as FDM is another different and common type of additive based technique. This method does not integrate the use of curing ultraviolet light in its fabrication approach, but a gradual deposition of thermally induced thermoplastic material commonly called "filament" through an extruding nozzle. This gradual deposition is enabled by electric motors for multidirectional motions. This thesis research is based on the process development of compliant structure mainly through FDM methods and provides a potential area of process enhancement and feature size refinement through stereolithography based methods.

Additive manufacturing is an emerging area of technology and numerous new research is currently ongoing to enable electronics industrial applications. Some of the benefits provided by additive manufacturing include:

- i. Opportunities for 3D manufacturing of complex designs

- ii. Opportunity for microstructural manufacturing

- Opportunity for cost and time effective methods of manufacturing by fabricating and prototyping high yield productions

- iv. Opportunity and avenue for manufacturing light-weighted parts, particularly helpfulin the Aerospace and Automotive industry

Table 2-1 below highlights some common additive manufacturing techniques, their working principle, and electronic fabrication applications. This table will provide references for applications that can be integrated into other electronics fabrication and give an insight into printing machine suppliers.

| Common<br>Additive<br>manufacturing<br>Technique | Printing<br>resolution<br>(μm) | Working<br>principle | Examples of fabricated electronic components | Major supplier/<br>Manufacturer | Reference  |

|--------------------------------------------------|--------------------------------|----------------------|----------------------------------------------|---------------------------------|------------|

| Inkjet                                           | ≥20                            | Ink deposition       | Inkjet printing of high-                     | Oasis 3DP                       | [24], [25] |

|                                                  |                                | based on a           | performance transistors                      |                                 |            |

|                                                  |                                | printing bed         |                                              |                                 |            |

|                                                  | ≥10                            | Atomization and      | Aerosol jet printing of phased               | Optomec                         | [24], [26] |

|                                                  |                                | vapor deposition     | array antenna                                |                                 |            |

|                                                  |                                | on the target        |                                              |                                 |            |

| Aerosol Jet                                      |                                | substrate            |                                              |                                 |            |

| Fused deposition                                 | 50 - 200                       | Forced filament      | 3D printing of electrical circuit            | Maker gear,                     | [27], [28] |

| model                                            |                                | extrusion via        | on a substrate                               | Prusa,                          |            |

|                                                  |                                | material melting     |                                              | Ultimaker                       |            |

| Stereolithography                                | 0.25 - 10                      | Ultraviolet light    | Embedded conductive wires and                | Formlabs,                       | [29], [30] |

| (SLA)                                            |                                | curing of liquid     | electronic components                        | Prusa                           |            |

|                                                  |                                | resins (thermoset    |                                              |                                 |            |

|                                                  |                                | plastics)            |                                              |                                 |            |

| Selective laser                                  | 22                             | Ultraviolet laser-   | Direct metal laser sintered Flat             | SLM Solutions                   | [31]-[33]  |

| melting (SLM)                                    |                                | based curing of      | finned heat sinks for electronics            | group                           |            |

|                                                  |                                | metallic powder      |                                              |                                 |            |

| Selective laser                                  | 20 - 150                       | Ultraviolet laser-   | Laser sintered Ag lines for                  | 3D systems                      | [34], [35] |

| sintering (SLS)                                  |                                | based curing of      | flexible electronics                         |                                 |            |

|                                                  |                                | thermoplastic,       |                                              |                                 |            |

|                                                  |                                | glass, and           |                                              |                                 |            |

|                                                  |                                | ceramics             |                                              |                                 |            |

| Binder jetting                                   | 35                             | Liquid binds         | Fabrication of dielectric radio              | Hewlett-                        | [36], [37] |

|                                                  |                                | selected powder      | frequency filters and ferroelectric          | Packard,                        |            |

|                                                  |                                | particles together   | dielectric capacitors                        | Digital Metal                   |            |

| Table 2-1: 3D printing techniques and application in electronics fabrication |  |

|------------------------------------------------------------------------------|--|

|------------------------------------------------------------------------------|--|

Electronics comprises conjoined material parts to make a device and the components of the devices may range from different classes of electrical materials such as conductors to aid electrical and signal connection, insulators to act as a dielectric of the device, and semiconductors commonly used in the fabrication of integrated circuits. The flexibility offered by additive manufacturing in the fabricating of co-manufactured materials provides a unique ability to simultaneously create electronic interconnects and structural elements comprising of insulators, conductors, and semiconductors.

#### 2.2 Electronics Packaging for Power Module Devices

Power device technologies include Silicon (Si), Silicon Carbide (SiC), Gallium Nitride (GaN) based transistors and they can be used to fabricate power Metal Oxide Semiconductor field-effect transistor (MOSFET) or Insulated Gate Bipolar transistor (IGBT) which are typically assembled and packaged on a substrate. Over the years, many requirements have influenced the research into the packaging of power modules, architectural assembly methods, and assembly materials.

Some of the concerns with module assembly and packaging are parasitic concerns and device reliability. Early methods of assembly power modules involved the use of wire bonds, which are the main causes of parasitic concerns, and they also cause poor thermal management schemes which inadvertently affect the overall reliability of devices particularly because of their architectural designs [10].

The main areas of focus for electrical and reliability improvements research can range between (1) improving cooling methods to curb extreme thermal conditions that pose structural and material property concerns especially at the interconnection points of the assembly and (2) implementing improved thermomechanical designs that can aid package withstanding extreme

stress conditions. This thesis focuses on the latter method of curbing these concerns albeit a manufacturing process is required to manufacture micro complex designs that can effectively meet the reliability requirements.

Development from wire bond methods of package and assembly for power modules have been improved by integrating flip chip technologies into power modules by Seal et al [10]. The flip-chip assembly method provides a great opportunity for enhancing electronics devices' capabilities but there are existing limits to power densification, improving switching frequency, etc. and this is hugely dependent on thermal management technologies. However, the architectural arrangement of components, material selection, and enhancement, structural designs, and integration are all important areas under emerging technologies curbing the effect of increased thermal energy generation and these areas of study are just as important as active and passive cooling and thermal management technologies and research.

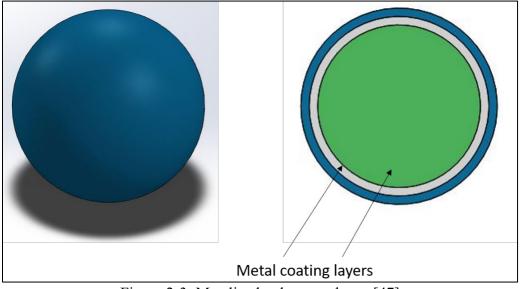

One of the main areas of focus in flip-chip fatigue life is the solder joint fatigue that occurs primarily due to solder ball cracking [38] and other secondary reasons such as intermetallic area growth [39] etc. To improve the mechanical strength of solder balls and further curb the rate of cracking of solder balls, researchers have developed several solder balls enhancing technologies and features typically to improve mechanical strain compliance in the device ranging from polymer cored balls [40], compliant interconnect, etc. where polymer cored balls are polymers coated in solders and compliant structures are structures that accommodate volumetric expansion effects and warpages in the device.

Many first-level compliant structures and designs have been developed in the last decade highlighting the potentials of this technology.

#### 2.3 Examples of Mechanical Enhanced Compliant Structure

#### i. Spring Based Interconnects

These are interconnects that particularly to reduce the impact of thermomechanical based interfacial stresses between assemblies by designing and developing microstructures with springlike properties i: e properties that can deflect under mechanical induced load with some mechanical stiffness. Many structures have these properties like a micro spring, cantilever beams, etc.

For example, Sitaraman et al., [41] developed the J spring shaped compliant interconnects using the photolithography and selective etching approach of fabrication in the cleanroom and other interconnect designs such as flex connect, arc-fan interconnects [42], smart three-axis compliant interconnect [43],  $\beta$ -Helix interconnect [44], etc. Compliant interconnect studies have shown solder fatigue life reliability improvements exemplified in [45] and [46] etc.

Figure 2-3: Metalized polymer spheres [47]

#### ii. Copper Bumps

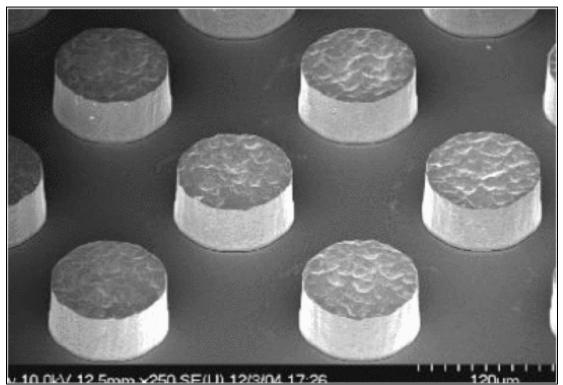

Copper bumps as the name implies, made of copper, making it a perfect material for integration between semi-conductors and substrates because of their closely aligned coefficient of thermal expansion, 16.7 ppm/ $^{0}$ C for Copper and 14 – 17 ppm/ $^{0}$ C for printed circuit boards and its great mechanical and thermal properties.

Micro copper pillars represent some of the early research done on the power device's reliability enhancement. These interconnects decouple the substrate from the die and are developed as a slender structure. The design of these structures is based on mechanical strength due to their bulking property without any form of mechanical compliance. The method of assembly for copper pillars and bumps is the metal post solder chip connection (MPS-C2) [48]. Many inventions have been generated from this technology like Intel [49], IBM [50], Powertech technology inc. [48], etc.

Figure 2-4: SEM images of copper bumps [51]

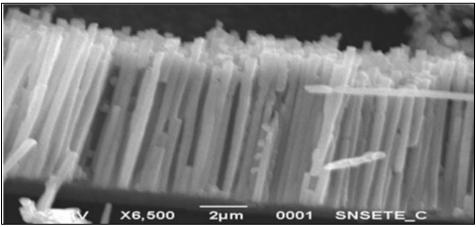

#### iii. Other Interconnects

Similarly, to copper bumps, there exists other interconnect bumps from other materials like carbon nanotube-based interconnects [52], copper nanowire bumps [53]. These other designs are a better alternative to compliance for copper bumps due to their design having a higher aspect ratio but they are inferior to copper bumps electrically due to their length, causing a higher self and mutual inductance in comparison to conventional copper bumps.

Figure 2-5: SEM images of copper nanowires [53]

Figure 2-6: SEM images of different compliant interconnect geometries G-Helix [54], Beta Helix [55], Flex connect [56]

Various compliant interconnect structures have been pursued in academia and industry and compliant interconnects researches have demonstrated mainly semi subtractive and subtractive approaches for fabrication which may greatly limit industrial application, due to limitation in complex compliant structures for improved reliability, manufacturing throughput, and adhesive stress regions, etc.

This work presents a novel additive fabrication approach directly on a printed circuit board and illustrates its mechanical properties and power module integration benefits, whilst also effectively improving device throughput and enabling complex structural fabrication. Complaint interconnects proposes a solution that reduces strain on solder joints but has its potential and advantages have not been fully harnessed due to current fabrication approaches, and throughput. This modal approach imitates casting [57] where the mold is removed after the development of the structures and components.

#### 2.4 Working Principle of Compliant Interconnects

Interconnects significance in an electronic device includes electrical performance and not just the mechanical and thermal benefits. The major cause of device failures in electronic devices is at the interconnects and components joints caused by the mismatch in the coefficient of thermal expansion. The coefficient of thermal expansion of printed circuit board (PCB) substrates is 17 ppm/°C which is very close with the CTE of copper, 17 ppm/°C. Therefore, copper is used in the design because it has a closer coefficient of thermal expansion to printed circuit boards (PCBs). Compliant interconnects are generally designed to reduce the risk of failure of solder balls either by introducing a composite like metalized polymer spheres or designing a mechanical structure to improve support and create an allowance for thermomechanical expansion, shock, and vibrations. In theory, during the interfacial expansion of package components joined by solder balls, there is a limited area available for the deformation allowed in the volume of solder ball leading to creeping and fatigue behaviors. This expansion of the different adjoined materials induces different stresses on the whole package due to different rates of expansion causing the

package to warp and solder joint fracture or failure in the long term. The thermomechanical effect of coefficient of thermal expansion mismatch occurs during extreme temperature conditions i: e extremely hot temperatures and extremely low temperatures,  $\Delta T$ , the effect of these values is dependent on the process temperature of the die attach during assembly typically the reflow temperature. Compliant interconnect designs curb the early failure susceptibility due to its thin cantilever design enabling the differential package expansion with lower stresses induced in the solder interconnects. This is evident as simulations (on Ansys®) show a lower maximum value of von mises stress in the overall device package for select designs. For the effective application of these components, some design conditions may be considered. Just as solder ball heights vary linearly across a die due to assembly conditions (warpage of the die during processing) and stress distribution reasons, we may adopt the same conditions during assembly of the interconnects. Interconnects can be designed on a board attachment to accommodate more stress at certain levels i:e interconnects close to the mid-region of a die can be designed to have low compliance while interconnects closer to the edges can be designed to have higher compliance [58] because the maximum shear and peeling stresses occur at the edges of a die [59]

#### **3. DESIGN FABRICATION APPROACH, AND METHODOLOGY**

Many efforts have been put into researching geometries and designs that can effectively meet the reliability challenges demands and 3D printing and additive manufacturing limitations. There are various design approaches such as 3-arc-fan compliant interconnect, micro j-springs, helix compliant, etc. [41], [60], [61].

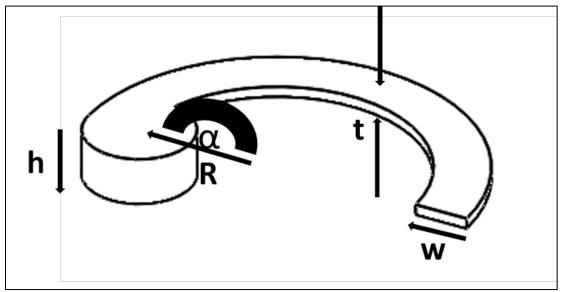

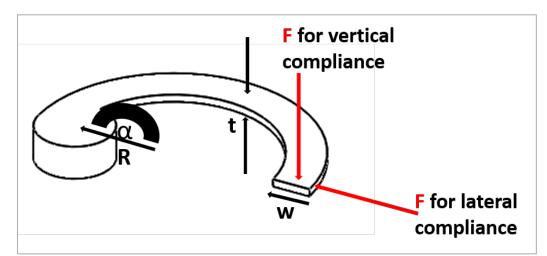

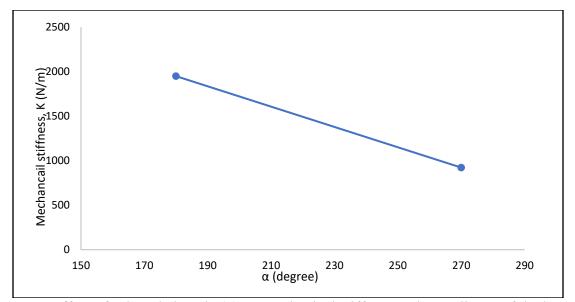

The design chosen is a cantilever beam shaped compliant structure additively manufactured directly on a printed circuit board (PCB) for fabrication and testing. This structure is chosen to enable proof of concept and the ability to integrate the novel additive based fabrication approach. The accuracy of fused deposition model-based printers requires the integration of a design to provide compliance whilst also working within the constraint of size. The cantilever beams are designed according to various variables which may or may not involve curved shaped cantilever beams. The study in this research has integrated the use of curly shaped beams to utilize their effect of better compliance whilst also optimizing the design space ranging from 90 to 330 degrees to enhance mechanical deflection and improve compliance. The selection of a particular geometry and shape of these interconnects depends on the interconnect's application and die's dimension. The beam's mechanical stiffness is characterized and compared with other literature designs for compliance applications.[62]

#### **3.1 Design Variables**

The interconnects are designed as a cantilever beam comprising of a copper post and a beam. The post will be manufactured and connected on a substrate and the top of the beams will be bonded to the die through soldering. The figure below, figure 3-1 shows variations in the design of these interconnects. The interconnects final design is dependent on the following variables: copper beam width, copper pad dimensions, copper beam thickness, copper post diameter,

copper post height and subtended angle all determine the overall surface area and footprint of each singular interconnects.

Figure 3-1: Additively manufactured interconnect model

### **3.1.2 Copper Post Variables**

The copper post variables directly affect the standoff or decoupling height between the die and substrate and affect the extent of deflection i: e out of plane compliance.

The effect of size and proximity of electrical interconnections in an electronic assembly on electronics parasitics encourages influences design conditions such as small copper posts, in both diameter and standoff height but due to current limitation of fused deposition model printing techniques inhibiting effective minimizing of these variables as very thin mold prints where the application of electrodeposition manufacturing technique is prevented due to porous prints for thin molds visible in figure 3-2. Also, FDM prints have limited printability of small hole sizes typically 0.5mm radius when using the 0.4 mm nozzle.

Figure 3-2: Image of a porous plot for thin molds

### 3.2 - Method of Fabrication

A new fabrication approach/ method which can reduce the cost of production of interconnects, reduce the number of steps and chemical processing required and effectively improve throughput is presented in this work.

Previous methods of fabricating compliant interconnects include the application of liquid photoresists and dry film photoresists which are essentially thin films. These thin films would require more than one in the fabrication of a microstructure consequently causing the addition of processing steps in the fabrication especially in the development of these films and concerns of film alignment, through UV light exposure and chemical development. Also, the application of dry films may not be very reliable as the films may undergo tear when being applied to the substrate board. Beyond the concerns of dry films, a liquid photoresist even poses more concerns as the application substrate must undergo heat treatment before use, such as a soft bake for curing of the photoresist and a hard bake is done after development to enhance the physical and chemical stability of the photoresist. These additional process for liquid photoresist poses a risk of failure to the substrate such as cracking of the photoresist, thus, reducing the application of the resist. Also, the above-mentioned fabrication reduces the use of cleanroom facilities and makes it easier to fabricate in almost any makeshift lab with little or no use or exposure to any chemical processing techniques.

The use of additive manufacturing in the fabrication of compliant interconnects for electronic devices is demonstrated by using a 3D printed mold as a support fabrication and sacrificial material designed and developed to be removed after fabrication.

#### **3.2.1 3D Printing Technique Selection**

There are numerous printing techniques, and they all have their merits and demerits. In general, the stereolithography method of printing provides more accurate and precise microprint when compared to the fused deposition model printing techniques. However, the SLA based printing technique is considerably inferior in material selection because most of the SLA based materials do not offer a material removable method either through melting or solvent solution. Even more so, materials that do offer opportunities for etching require melting at very high temperatures > 200 C for some select materials which is not an ideal processing environment for FR4 printed circuit boards with ideal operating temperature -50 -110 C. Extensive study done on 3D printing materials and mode of printing enabled a decisive conclusion on using FDM based techniques due to the material etching requirement.

# **3.2.2 Material Selection**

Establishing a 3D printing technique requires a material study on probable integrating materials to enable proof of concept and application. Many materials have been characterized and compared for application to the fabrication methodology across the two major 3D printing techniques and select material properties are highlighted in table 3-1.

|                        |                    | 1            | 1          | e           |            |

|------------------------|--------------------|--------------|------------|-------------|------------|

| Material<br>Properties | Castable De<br>wax | ental Resin  | BVOH       | PLA         | ABS        |

| Melting                | 46 - 68            | 41 - 48      | 200 - 230  | 185 - 205   | 220 - 250  |

| Temperature            |                    |              |            |             |            |

| ° C                    |                    |              |            |             |            |

| Process                | Irreversible       | Irreversible | Reversible | Reversible  | Reversible |

| Reversibility          |                    |              |            |             |            |

| Solvent                | None               | None         | Water      | Sodium      | Acetone    |

|                        |                    |              |            | Hydroxide   |            |

| Copper                 | No                 | No           | Absorb     | No Reaction | No         |

| Sulphate               | Reaction           | Reaction     | solution   |             | Reaction   |

| Reaction               |                    |              |            |             |            |

| Print Method           | SLA                | SLA          | FDM        | FDM         | FDM        |

| Filament               | \$\$\$             | \$\$\$       | \$\$       | \$          | \$         |

| Cost                   |                    |              |            |             |            |

After careful material study and characterization for this process development, few materials meet the process requirement and application development to manufacturing these interconnects, a water-soluble based material (BVOH) and an acetone soluble material (ABS).

These materials would enable the printing of a negative imaged print of the desired structures. A negative print or structure are structures that enable the development of a structure by providing an open path within itself for material deposition. The selected materials will aid the layer deposition of our select material to form the desired negative shape. Through the mold, copper will be deposited via electrodeposition/ electroplating and will be formed through the exposed negative mold. This method of gradually depositing copper is reliable because the properties of the deposited copper are consistent with the ideal properties of copper. Common problems faced in other metal additive approach includes porous deposition and poor density of the fabricated structures highlighting further this technique encourages better deposition through reduced porosity which can affect their material property.

Also, this technique is relatively cheaper because the whole process occurs within room temperature compared to other additive manufacturing techniques that have high manufacturing temperatures causing probable damage to a printed circuit board. In this approach, to arrive at a highly resolved and cost-feasible approach, the integration of two main technologies is observed, fused deposition model 3D printing and chemical electroplating.

25

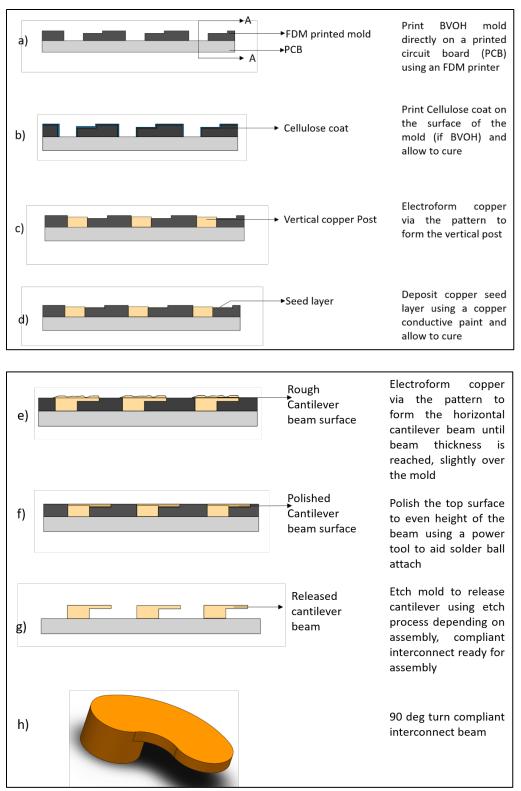

Figure 3-3: Process flow for additive manufacturing of compliant interconnects

#### 3.2.3 – ABS Method of Fabrication Overview

The mold is printed with Acrylonitrile Butadiene Styrene (ABS) using a Prusa MK I3 fused deposition model printer at the normal printing requirements for ABS, 90°C build plate, bed temperature, and 240°C hot end/nozzle end temperature. To get better print quality and accuracy, the printer speed is reduced to 30mm/s and a 400µm diameter nozzle is installed.

a. The structures are designed in a negative mold using a solid modeling tool and the sliced .stl file is 3D printed directly on a printed circuit board. A negative image/mold of a structure is an inversed structure that aids the development of the proposed structure by filling the cavity in the negative mold, after which the mold is removed, identical to investment casting. The printer's offset z-height has been calibrated to accommodate the PCB.

Figure 3-4: Pictorial image of 3D FDM printer printing on a PCB

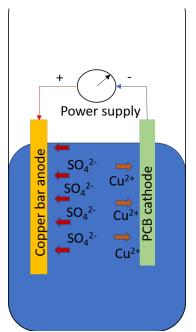

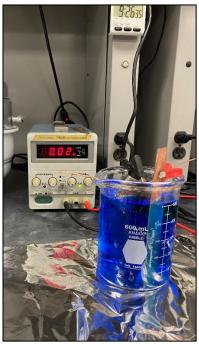

b. The electroplating setup is prepared comprising of a Copper sulfate solution in a (500ml) glass beaker. A copper bar (155mm x 24mm x 1mm) is connected as the anode while the sample preparation from step a is connected as the cathode. A 30V tetronix PS821 DC power supply is used to provide a current of 0.01 ampere and 0.2 volts to the setup and the vertical copper bump is electrodeposited until initial post height is attained to enable electrical continuity for the horizontal beam. The electrical parameters are decided with the following equation below.

Following the rule of thumb of electroplating with optimum electroplating current at 0.2Amps/inch<sup>2</sup> translated to 0.00031 Amps/mm<sup>2</sup>.

The current is determined by measuring the exposed surface area from the negative molds.

$$nA * 0.00031 = I_m$$

$$A = \pi r^2$$

Where n is the number of exposed regions for the copper post

A is the surface area of one exposed pad

r is the radius of the exposed area

Im is the current recommended for electroplating the sample

Equation 3-1: Current calculating equations for electroplating

Figure 3-5: Electrical electrodeposition set up

c. The electrodeposition process is divided into two steps. The first step, b takes advantage of copper on the top surface of the PCB using that as step 1's seed layer. The second step involves the fabrication of the beam. To aid the electrodeposition of copper on the printed mold, the electrodeposition is stopped, and a Caswell-plating copper conductive paint is applied as the copper seed layer using a 200µm laser cut stencil and allowed to dry for 60 minutes to aid electrical continuity between the copper post to the mold.

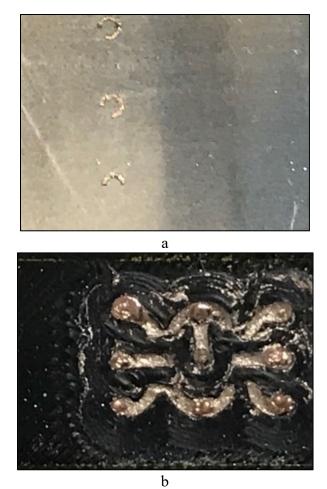

Figure 3-6: Electrodeposited copper post

Figure 3-7: (a) stencil image after the printing of horizontal seed copper layer (b) Image of applied conductive paint

The electrodeposition process is restarted, and the horizontal beam is electrodeposited although at a much slower rate to the deposition of the copper post to help reduce the surface roughness of the pads

f. After the process and sample refinement, the mold is removed by placing the sample in a bath of Acetone as ABS is soluble in Acetone. After the complete dissolving of the ABS material, the free-standing interconnect can be seen and ready for assembly.

Figure 3-8: (a) Image of fabricated compliant interconnects within the mold (b) Image of compliant interconnects after mold removal

# 3.2.4 – BVOH Method of Fabrication Overview

Here we use a 3D printer (Creality Ender 3) a fused deposition modeling printer. The printer 180mm/s. The material used to print the mold is butenediol vinyl alcohol co-polymer (BVOH) which is majorly used as a support material for other 3D printing projects. The printing temperature of the BVOH is about 220°C before extrusion begins, the printer is generally

equipped with a 0.4mm nozzle but to get improved resolution, a 0.2mm nozzle diameter is installed.

- A .stl file of the mold containing a negative image of the compliant structure(s) is 3D printed directly on a printed circuit board after calibrating the appropriate offset distance between the print bed and the nozzle.

- b. The mold is painted with a coating (Nitrocellulose), to prevent the copper sulphate absorption by the BVOH mold and allowed to dry.

Figure 3-9: (a) BVOH print without cellulose coat (b) BVOH print with cellulose coat

Just as the ABS method, the steps after b, is followed with a slight difference between the next steps of the BVOH and ABS discussed below

- i. The degradation of the BVOH material makes the deposition process of this material considerably slower and the optimal growth rate is  $5.85 \times 10^{-4} \text{ mm}^3/\text{min}$  for the copper post.

- The mold is dried at ambient room temperature before the next feature plating and before the application of the seed layer i: e Caswell-plating copper conductive paint. The paint is applied on the design path printed (horizontally) using a 200 µm thick laser cut stencil and allowed to dry for 1 hour.

- iii. The setup is started again to allow the off-chip structure to grow for about 2 3 hours depending on the geometrical design. This has a slower growth rate of  $2 \times 10^{-3}$  mm<sup>3</sup>/min to also help reduce the surface roughness of the pad

f. After the process and sample refinement, the mold is removed by placing the sample in a bath of Acetone to remove the cellulose coat and after complete removal of the cellulose coat, the mold is placed in a beaker of warm distilled water at about  $(40 - 60^{\circ} \text{ C})$  and a sonicator may be used to agitate the water and consequently increase etching of the mold thus exposing the free-standing interconnect can be seen and ready for assembly.

#### 3.3 – Process Refinement

At this stage, the interconnect has been fabricated but some post-fabrication process refinement, step e needs to be done before step f.

Some of the major concerns that are corrected with the post-refinement process are:

- Beam surface roughness for solder flux and reflow

33

- Design and fabrication dimension/shape accuracy for precise mechanical (in-plane and outplane) and electrical characterization and prediction.

After step d, the cleanroom photo-etching process is done on the fabricated structures before removal of the mold.

1. The sample is polished using a Dremel power tool polisher until even surface height is visible and the surface is smooth enough for solder ball attach.

Figure 3-10: Power polishing tool

2. A negative photomask is printed used for ultraviolet light exposure of the photoresist on the beams and is laminated on the sample for etching.

Figure 3-11: Printed negative photomask on a fabricated sample

After exposure, the photoresist is developed in a Sodium Carbonate bath and the sample is later placed in a conveyor Chemcut SA2315 spray etcher containing ferric chloride and ran for 2 cycles.

Figure 3-12: Exposed dry film on a fabricated sample

4. After the etching of the copper, the photoresist is removed using a bath of Isopropyl alcohol. In the cleanroom photoresist process, step 1 is repeated using a liquid photoresist on the interconnect pads to identify and earmark points for solder placement during assembly.

Figure 3-13: Optical images of interconnects (a) before polishing (b) after polishing

# 3.4 – Assembly

The assembly process is identical to the conventional flip-chip assembly method with the use of solder flux, a mechanical alignment fixture to prevent displacement from shock, and a reflow oven.

The Sikama falcon 5c reflow profile for SAC 305 was adopted from its preset temperature profile [63], [64].

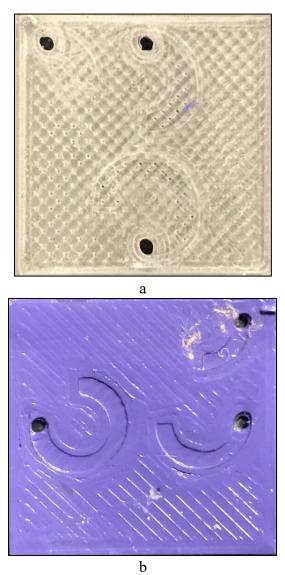

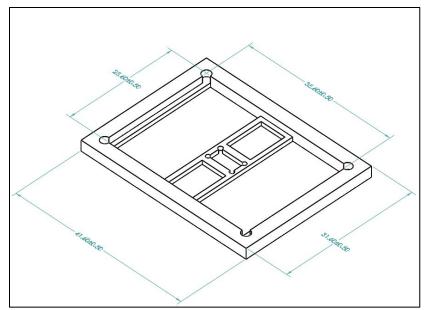

Figure 3-14: Die assembly mechanical fixture design

The fixture is designed with edge tolerance to allow proper placement in the design. The fixture has two designs and fixtures area, one to hold the die and the other to hold the substrate while also accounting for the height of the interconnect.

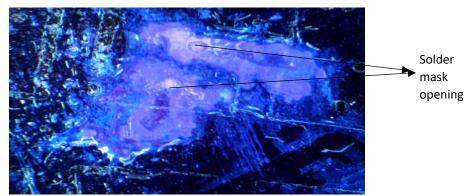

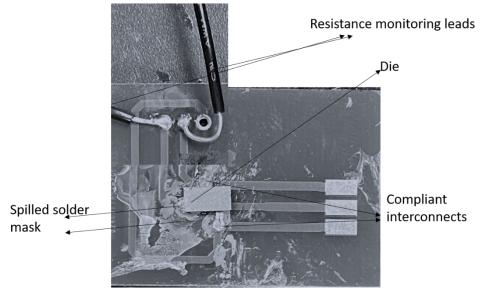

Firstly, the die is prepared in the cleanroom by attaching the solder mask for solder placement. Solder flux Kester TSF-6522 is then applied over the interconnect and allowed to dry and the solder balls, 305 mm in diameter are placed precisely with the aid of a solder mask, and a mechanical fixture is used to prevent the die from being displaced.

Figure 3-15: Solder mask opening on interconnect

The mechanical fixture is machined from graphite to aid effective heat transfer from the top end of the reflow oven through the die for solder reflow.

The SAC 305 reflow profile is selected for the solder reflow with reflow properties shown in table 3-2.

| Time (sec)         | Temperature (C) |

|--------------------|-----------------|

| 0 – 90 (Preheat)   | 25 - 150        |

| 90 – 180 (Soak)    | 150 - 180       |

| 180 – 240 (Reflow) | 180 - 220       |

| 240 – 270 (Cool    | 220 - 150       |

| down)              |                 |

Table 3-2: SAC 305 solder ball reflow temperature profile

Figure 3:16 Assembled device for testing

## 3.5 Process and Material Characterization

The materials within the process are characterized to understand the interactions within the process and how these reactions can affect the reliability of the process, manufacturing parameters, or even design conditions to account for and if there are any material degradation such as swelling, etching, etc.

## 3.5.1 – BVOH Characterization

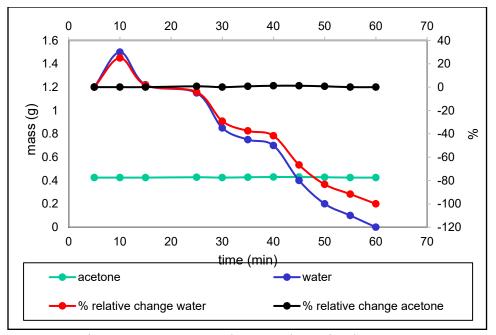

BVOH is a water-soluble material and therefore becomes unreliable when in contact with liquids and reacts differently to different solvents. Here, the study of how BVOH reacts in all the working fluids used in this process such as Acetone, Copper Sulphate solution, and deionized water is presented.

The BVOH is characterized to understand the standard degradation time per mass of mold which can be integrated to optimize the volume of the structure being fabricated and enable decision in electrical parameters for faster deposition within the mold's durable period and before degradation.

This process is characterized by weight measurement of a sample of BVOH before and after interval time in the various test solution

Figure 3-17: Weight measuring apparatus

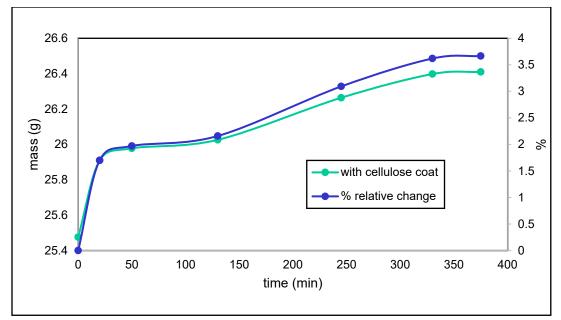

Figure 3-18: BVOH etch rate and reaction in acetone

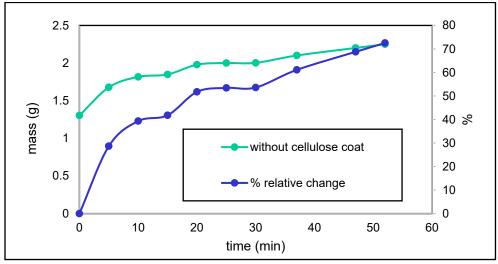

Figure 3-19: BVOH copper sulphate absorption rate without cellulose coating

Figure 3-20: Partially coated BVOH absorption rate

As illustrated in the charts above, the BVOH absorbs the copper sulphate liquid and this is observed by the increase in the mass of the sample over time, hence the use of the cellulose coat to reduce the absorption rate of the BVOH. One of the major drawbacks of this solution absorption is the effect it has on the electroforming quality. Little or no copper is deposited through the mold when the BVOH expands due to solution absorption as the cavities printed in the mold would be blocked.

The application of the cellulose coat slows down the absorption rate and allows the integrity of the mold for the electrodeposition of the copper post for a couple of hours before swelling starts to occur.

BVOH is relatively stable in acetone and there is no significant mass change when left in acetone. In figure 3-15, we can see that the BVOH readily dissolves in water and can easily absorb moisture when left open without desiccants

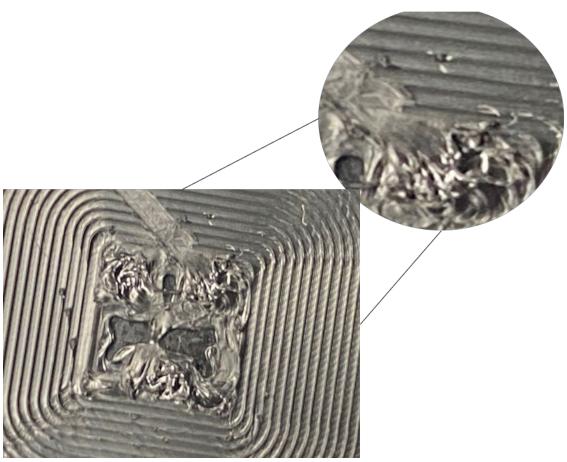

## 3.5.1.1 BVOH Mold Negative Path Degradation

Here, a 3D printed mold is characterized for physical degradation by optical observation in the changes in the mechanical structural integrity of the mold, thus affecting the fabrication process. Although the cellulose coat can slow down material degradation, if electrodeposition is too slow, copper sulphate will eventually penetrate the mold. Figure 3-18 below shows a soggy coated and uncoated BVOH mold to illustrate the unreliability of this material.

Figure 3-21: Visible degradation during electrodeposition of BVOH (a) Without coating (b) With coating

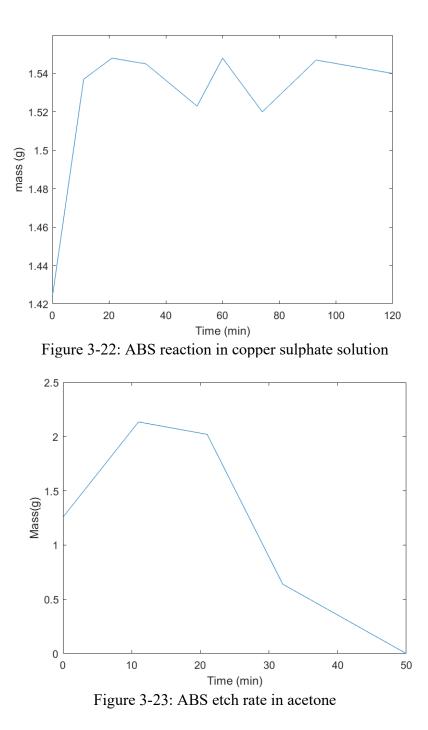

## 3.5.2 – ABS Characterization

A concurrent study on ABS is also done by characterizing its reaction within the working fluids as a comparison to BVOH. The characterization of ABS is done to establish an understanding of material reaction and effect that can affect the design and electrodepositing parameters. ABS is readily soluble in acetone and copper sulphate does not have a huge impact on ABS. The chart below shows that ABS does not absorb the copper sulphate solution evident from the little change in mass of the ABS material with time in fluid and thus the design and manufacturing conditions do not need to alter.

Since there is no visible mass change of the ABS material in the copper sulphate, the integrity of the material is thus stable for uninterrupted additive deposition of copper and thus, no further study of the material mold shape degradation is required.

#### 4. INTERCONNECT MODELLING AND CHARACTERIZATION

#### (Modeling and Simulation)

Multiple arrays of interconnects have been fabricated and characterized for their compliance capability to determine their mechanical stiffness. Experimental test setups are validated by mechanical modeling and simulations.

The materials are modeled to match operating conditions and material behaviors including linear, nonlinear, elastic, and inelastic behaviors.

#### 4.1 - Material Modeling

To accurately understand the overall impact of these structural enhancing technologies, there is a need to understand the fundamental behavior of the package during thermomechanical loading, representing real-life operating conditions.

Typically, mechanical loading may be linear and nonlinear. The materials used in the modeling of the packages include Flame repellant 4 printed circuit board (FR4), copper, lead-based solder, Pb37Sn63, and silicon carbide die.

## 4.1.1 - Solder

Solder is modeled as a Viscoplastic material due to its constitutive behavior under stress where solder behaves more linearly than linear causing an inability to go back to its original undeformed shape after loading describing its inelastic behavior.

To replicate the mechanical behavior of this material, Anand's model is used to model the solder ball's nonlinear behavior and the input parameters are illustrated in table 4 -1.

$$\frac{d\varepsilon_p}{dt} = Ae^{\left(-\frac{Q}{Rt}\right)} \left[\sinh\left(\frac{\xi}{s}\frac{\sigma}{s}\right)\right]^{\frac{1}{m}}$$

Where  $\dot{s} = \left[Signh_0 \left|1 - \frac{s_0}{\hat{s}}\right|^a\right] \cdot \dot{\varepsilon}_p$

And  $\hat{s} = \hat{s} \left[\frac{\varepsilon_p}{A}e^{(Q/RT)}\right]^n$

# Table 4-1: Anand's parameters for Pb37Sn63

Anand's parameters for Pb37Sn63

| Poisson's ratio                                                | V   | 0.38                 |

|----------------------------------------------------------------|-----|----------------------|

| The initial value of deformation resistance                    | So  | 1.241E+              |

|                                                                |     | 07 MPA               |

| Activation Energy/ Universal gas constant                      | Q/R | 9400 K <sup>-1</sup> |

| Pre-exponential factor                                         | А   | 4E+06                |

| Multiplier of stress                                           | لاح | 1.5                  |

| Strain rate sensitivity of stress                              | m   | 0.303                |