#### University of Arkansas, Fayetteville

# ScholarWorks@UARK

Theses and Dissertations

7-2020

# Towards High Efficiency and High Power Density Converter: System Level Design, Modulation, and Active EMI Filters

Hongwu Peng University of Arkansas, Fayetteville

Follow this and additional works at: https://scholarworks.uark.edu/etd

Part of the Controls and Control Theory Commons, and the Power and Energy Commons

#### Citation

Peng, H. (2020). Towards High Efficiency and High Power Density Converter: System Level Design, Modulation, and Active EMI Filters. Theses and Dissertations Retrieved from https://scholarworks.uark.edu/etd/3795

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact ccmiddle@uark.edu.

## Towards High Efficiency and High Power Density Converter: System Level Design, Modulation, and Active EMI Filters

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

by

Hongwu Peng Huazhong University of Science and Technology Bachelor of Science in Electrical and Electronics Engineering, 2018

## July 2020 University of Arkansas

| This thesis is approved for recommendation to the Graduate Council. |  |  |

|---------------------------------------------------------------------|--|--|

|                                                                     |  |  |

| Roy McCann, Ph.D.                                                   |  |  |

|                                                                     |  |  |

#### **Abstract**

Power converter exposes strong challenges to its efficiency, power density and reliability. For the grid-connected inverter application, three-level (3-L) T-type neutral-point-clamped (TNPC) inverters has higher efficiency and lower total harmonic distortion (THD) compared to two-level inverter. Hybrid switch concept combines the benefit of both silicon carbide (SiC) MOSFET and Si IGBT. By applying hybrid switch structure in 3-L T-type inverter, the total power density of 3-L TNPC inverter will be higher while the cost will be lower than that of all-SiC 3-L T-type inverter. The hybrid switch based 3-L TNPC inverter also imposes challenge to its modulation and control, a propoer modulation and control sheeme need to be chosen to enable better inverter performance in terms of efficiency, neutral point balancing and electromagnetic interference (EMI). Morever, to shrink the EMI filter size for the power converter, an active EMI filter (AEF) structure is proposed. The proposed AEF provides superior performance than any of the conventional passive EMI filter and the existing AEFs. In this work, the system level design and testing of a 30 kW grid-connected 3-L T-type inverter with hybrid switch structure is discussed. Then, an improved space vector modulation (SVM) has been proposed, which enables neutral-point balancing (NPB) control in the proposed hybrid-switch-based TNPC inverters with loss and common-mode voltage reduction. Finally, the design, modelling, and testing of the proposed AEF is demonstrated.

#### Acknowledgment

I would like to thank Dr.Fang Luo for offering me the chance to fulfill my master's degree under his supervision. I'm grateful for the training and advice he has provided to me as a graduate student.

I would like to thanks my committee members Dr. Yue Zhao and Dr. Roy McCann for the support the suggestion to improve my work in master thesis.

I would like to thank my lab colleagues for helping me with the learning and testing. Without them, I would not have finished such many projects in this two year journey. I would like to thank Zhao Yuan, Balaji Narayanasamy, Asif Imran Emon, Amol Deshpande, Riya Paul, and all undergraduate and graduate students who worked with me in the past 2 years.

# **Dedication**

This work is dedicated to my parents (names are not included for privacy) for supporting me through childhood to adult. I am also thankful to my future wife for not being present in my life till now, so I could dedicated on research.

# **Table of Contents**

| 1 | Intro | duction                                                                                                     | 1  |

|---|-------|-------------------------------------------------------------------------------------------------------------|----|

| 2 |       | tical Design and Evaluation of a High Efficiency 30-kVA Grid Connected PV Iner with Hybrid Switch Structure | 3  |

|   | 2.2   | Introduction                                                                                                | 3  |

|   | 2.3   | System Level Design and Optimization                                                                        | 4  |

|   |       | 2.3.1 Inverter Topology and Semiconductor Stage Evaluation                                                  | 6  |

|   |       | 2.3.2 LCL filter Design                                                                                     | 8  |

|   |       | 2.3.3 DC-link capacitor                                                                                     | 13 |

|   | 2.4   | Hardware Development and Experiment                                                                         | 14 |

|   | 2.5   | Conclusion                                                                                                  | 17 |

|   | 2.6   | Bibliography                                                                                                | 19 |

| 3 | Spac  | ee Vector Modulation for Neutral-Point Balancing Control in Hybrid -Switch-Based                            |    |

|   | -     | be Neutral-Point-Clamped Inverters With Loss and Common-Mode Voltage Reduction                              | 21 |

|   | 3.1   |                                                                                                             | 21 |

|   | 3.2   | Introduction                                                                                                | 21 |

|   | 3.3   | Analysis of Different Modulation on Hybrid Switch Based 3-Phase 3-L TNPC                                    | 24 |

|   |       | 3.3.1 Preferred Switch Pairs in Terms of Switching Loss Reduction                                           | 25 |

|   |       | 3.3.2 Common Mode Voltage of 3L TNPC Inverter                                                               | 26 |

|   |       | 3.3.3 Switching Loss Reduction, NPB, and CM Voltage Analysis for Different                                  |    |

|   |       | SVM Schemes                                                                                                 | 27 |

|   | 3.4   | Experimental Test and Loss Breakdown                                                                        | 30 |

|   | 3.5   | Conclusion                                                                                                  | 37 |

|   | 3.6   | Bibliography                                                                                                | 39 |

| 4 | Sele  | ctive Digital Active EMI filtering using Resonant Controller                                                | 43 |

|   | 4.1   | Abstract                                                                                                    | 43 |

|   | 4.2   | Introduction                                                                                                | 43 |

|   | 4.3   | Active EMI filter Topology and System Level Modeling                                                        | 46 |

|   | 4.4   | Detailed Modeling of Digital Resonant Controller and Circuit Elements                                       | 49 |

|   |       | 4.4.1 Discretization Methods of Resonant Controller                                                         | 50 |

|   |       | 4.4.2 Gain Selection for Resonant Controller                                                                |    |

|   |       | 4.4.3 Modeling of The High Pass Filter                                                                      | 52 |

|   |       | 4.4.4 modeling of the ADC and DAC Sampling System                                                           | 53 |

|   | 4.5   | Design Example of the Proposed Concept and VNA Measurement for Stability                                    |    |

|   |       | Analysis                                                                                                    | 54 |

|   | 4.6   | Experimental Results                                                                                        | 59 |

|   |       | 4.6.1 Small-Signal EMI Test                                                                                 | 59 |

|   | . –   | 4.6.2 Converter EMI Test Results                                                                            | 60 |

|   | 4.7   | e                                                                                                           | 62 |

|   | 4.8   | Bibliography                                                                                                | 63 |

| 5 | Conclusion and Future Work           | 65 |

|---|--------------------------------------|----|

| A | List of published and submitted work | 66 |

# **List of Figures**

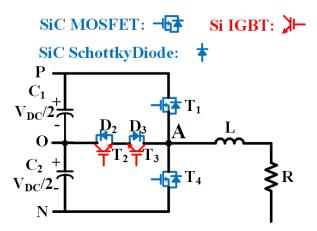

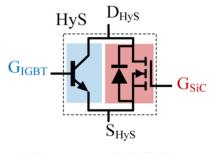

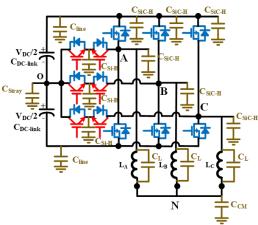

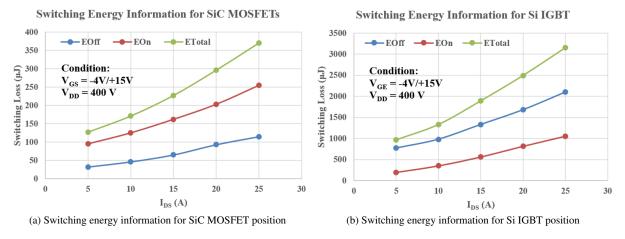

| Fig. 2.1:  | A hybrid switch based TNPC structure[4]                                                                                                                                        | 4  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

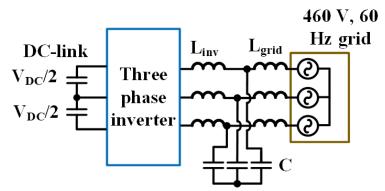

| Fig. 2.2:  | Three phase grid connected inverter                                                                                                                                            | 5  |

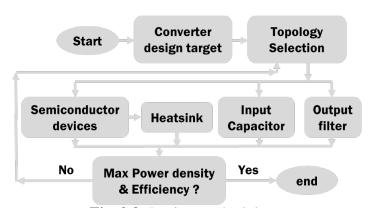

| Fig. 2.3:  | Design methodology                                                                                                                                                             | 5  |

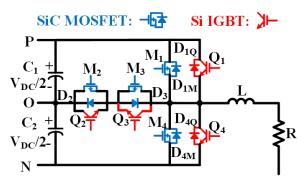

| Fig. 2.4:  | Evaluated converter topologies: (a) 2-L 3 phase inverter (b) 3-L 3 phase NPC inverter (c) 3-L 3 phase TNPC inverter (d) 3-L 3 phase TNPC inverter with hybrid switch structure | 7  |

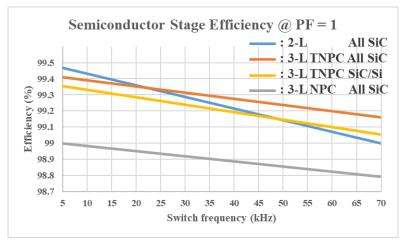

| Fig. 2.5:  | Semiconductor stage efficiency comparison                                                                                                                                      | 10 |

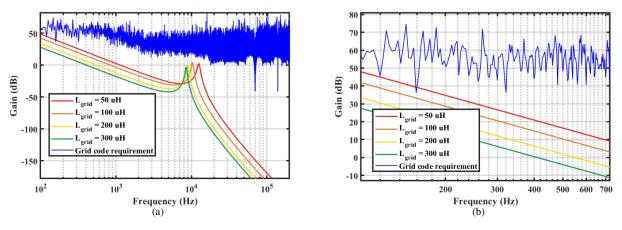

| Fig. 2.6:  | LCL filter design in frequency domain: (a) attenuation of LCL filter comparing to required attenuation (b) zoom in of low frequency range                                      | 11 |

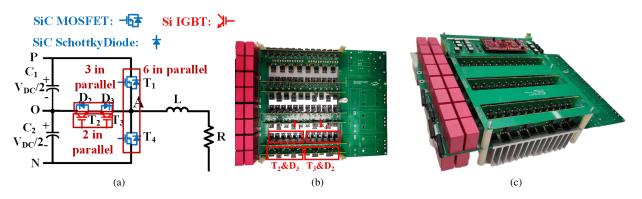

| Fig. 2.7:  | Hardware prototype for 3 phase 3-L inverter with hybrid switch structure: (a) Structure of 3-L TNPC phase leg (b) Top view of prototype (c) 3-phase 3-L TNPC inverter          | 15 |

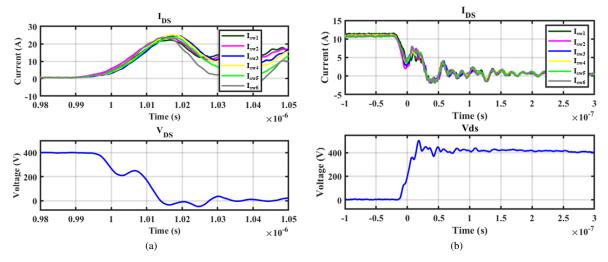

| Fig. 2.8:  | DPT test waveform for $T_4$ device: (a) Turn on transient of $T_4$ position (b) Turn off transient of $T_4$ position                                                           | 15 |

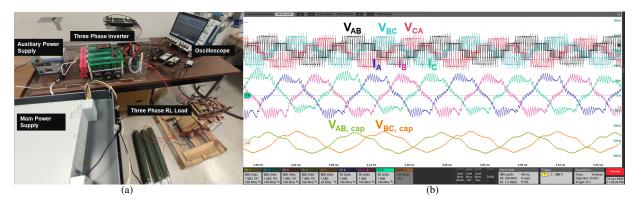

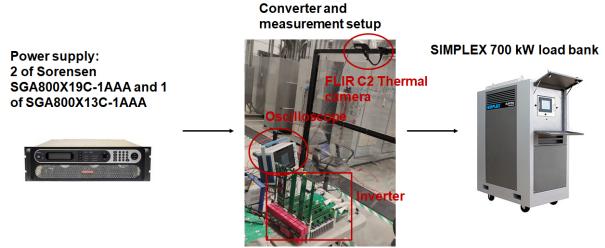

| Fig. 2.9:  | Continuous test for 3 phase 3-L TNPC prototype: (a) Test setup for 3 phase testing (b) Testing waveform                                                                        | 16 |

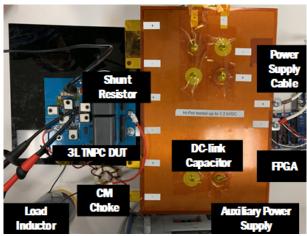

| Fig. 2.10: | Resistive load testing setup                                                                                                                                                   | 16 |

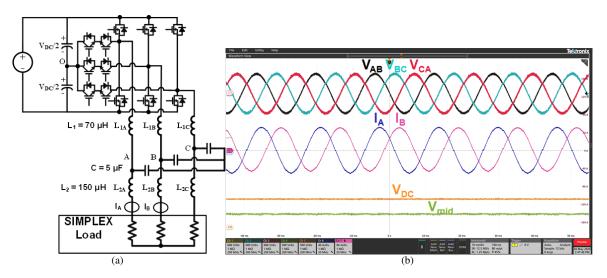

| Fig. 2.11: | Resistive load testing: (a) Resistive load testing schematic (b) Resistive load testing waveform                                                                               | 17 |

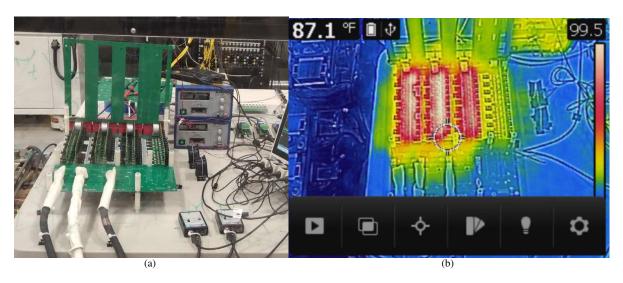

| Fig. 2.12: | Thermal image of the resistive load test: (a) original test setup (b) thermal image                                                                                            | 18 |

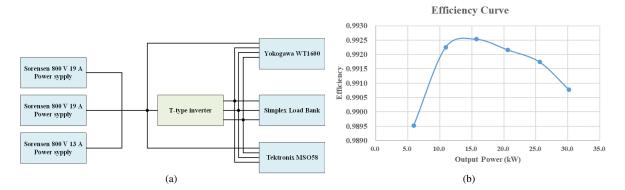

| Fig. 2.13: | Efficiency measurement of the inverter: (a) Efficiency measurement setup (b) Efficiency measured                                                                               | 18 |

| Fig. 3.1:  | Structure of the hybrid switch                                                                                                                                                 | 22 |

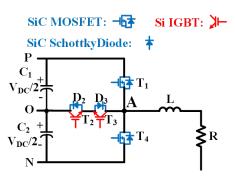

| Fig. 3.2:  | T-type inverter with hybrid switch structure 1 [13]                                                                                                                            | 22 |

| Fig. 3.3:  | T-type inverter with hybrid switch structure 2 [21]                                                                                                                            | 23 |

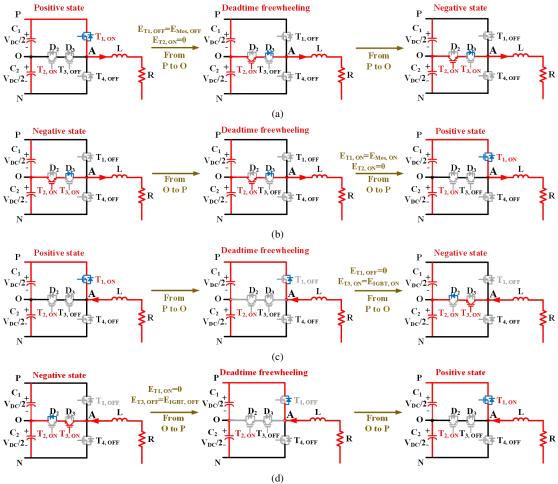

| Fig. 3.4:  | Different switching transitions when the phase output is positive or neutral: (a) Switch transition 1 (Positive phase current) (b) Switch transition 2 (Positive phase current) (c) Switch transition 3 (Negative phase current) (d) Switch transition 4 (Negative phase current) | 25 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 3.5:  | Three-phase 3-L TNPC model with the parasitic capacitor                                                                                                                                                                                                                           | 27 |

| Fig. 3.6:  | Three-phase 3-L TNPC CMV path                                                                                                                                                                                                                                                     | 27 |

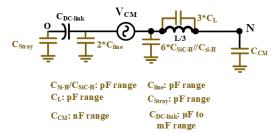

| Fig. 3.7:  | Three-phase three-level space vector hexagon                                                                                                                                                                                                                                      | 28 |

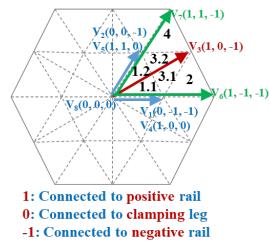

| Fig. 3.8:  | Switching loss information for SiC MOSFET position and Si IGBT position .                                                                                                                                                                                                         | 30 |

| Fig. 3.9:  | Test setup of DPT                                                                                                                                                                                                                                                                 | 31 |

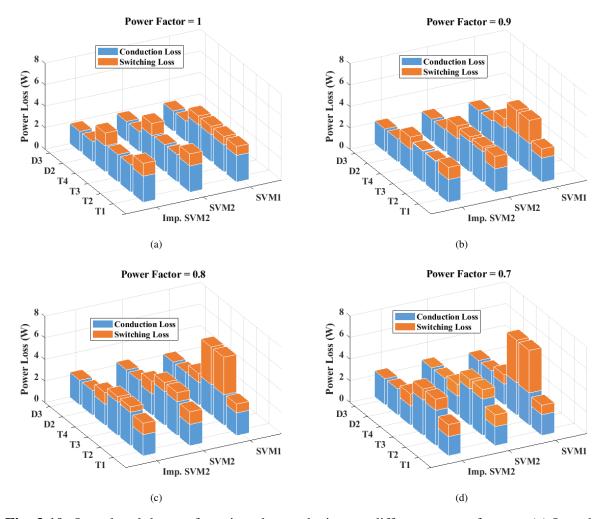

| Fig. 3.10: | Loss breakdown of semiconductor devices at different power factors: (a) Loss breakdown when PF=1 (b) Loss breakdown when PF=0.9 (c) Loss breakdown when PF=0.8 (d) Loss breakdown when PF=0.7                                                                                     | 32 |

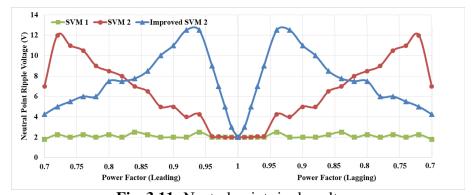

| Fig. 3.11: | Neutral point ripple voltage                                                                                                                                                                                                                                                      | 33 |

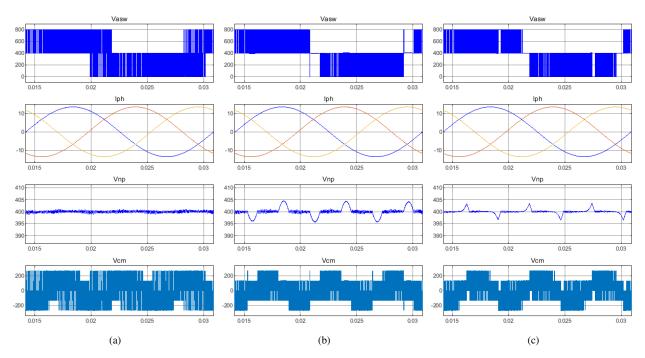

| Fig. 3.12: | Phase leg output voltage, phase current, NP voltage, and CM voltage waveform when PF=0.8: (a) Waveform for the SVM 1 (b) Waveform for the SVM 2 (c) Waveform for improved SVM 2                                                                                                   | 34 |

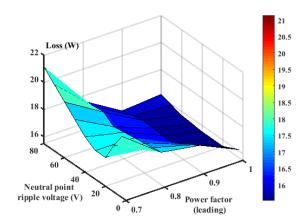

| Fig. 3.13: | Trade-off between NPB and loss performance for improved SVM 2                                                                                                                                                                                                                     | 35 |

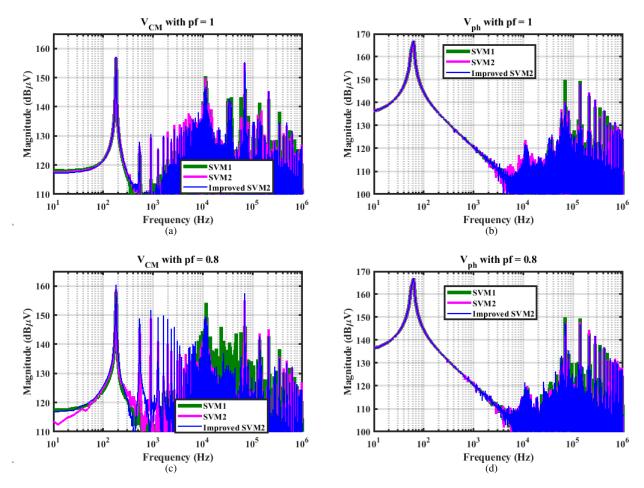

| Fig. 3.14: | CMV and phase voltage spectrum at different power factors: (a) CMV when PF=1 (b) Phase voltage spectrum when PF=1 (c) CMV when PF=0.8 (d) Phase voltage spectrum when PF=0.8                                                                                                      | 36 |

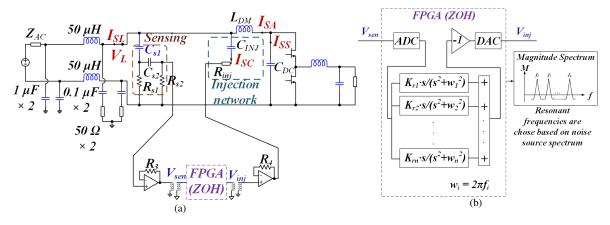

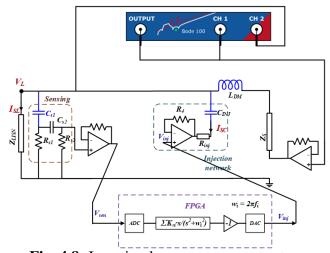

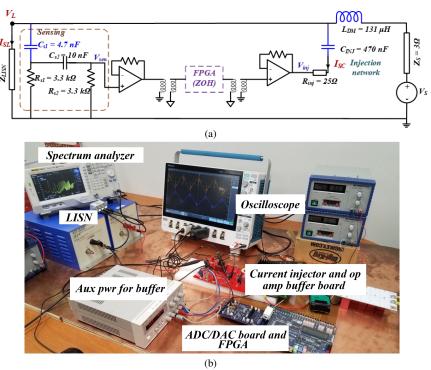

| Fig. 4.1:  | Proposed digital active EMI filter with the resonant controller: (a) Digital active EMI filter based on VSCC topology (b) Resonant controller built in FPGA                                                                                                                       | 44 |

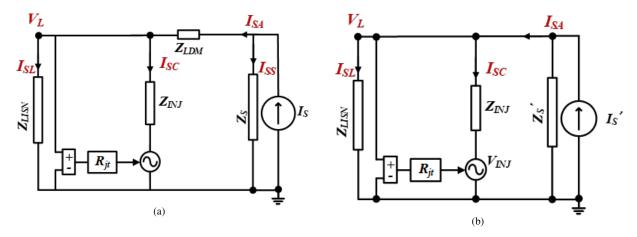

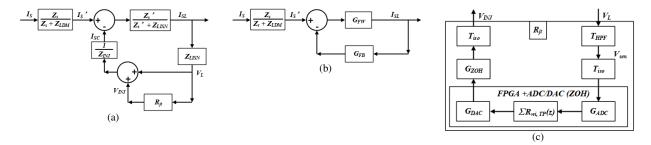

| Fig. 4.2:  | VSCC AEF topology: (a) Simplified VSCC AEF topology (b) Equivalent circuit of VSCC AEF topology                                                                                                                                                                                   | 47 |

| Fig. 4.3:  | Block diagram of the VSCC DAEF system: (a) System block diagram (Sensing and FPGA processing stage are collapsed into $R_{jt}$ ) (b) Equivalent system block diagram (c) Sensing and FPGA processing stage block diagram                                                          | 48 |

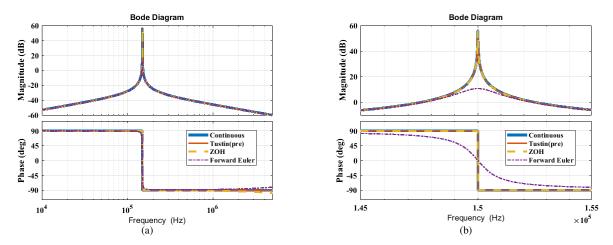

| Fig. 4.4:  | Gain and phase comparison of different discretization methods: (a) Comparison within 10 kHz to 10 MHz (b) Comparison within 145 kHz to 155 kHz                                                                                                                                    | 51 |

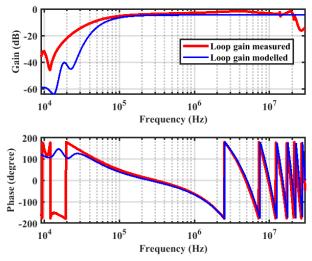

| Fig. 4.5:  | Loop gain without resonant controller                                                                                                                                                                                                                                             | 56 |

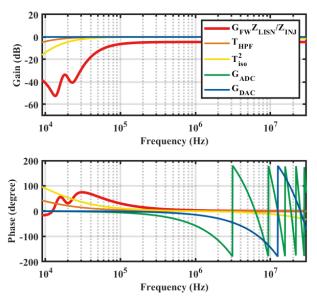

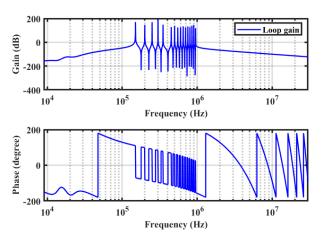

| Fig. 4.6:  | The bode plot of each transfer function                                                                                                                                                                                                                                           | 57 |

| Fig. 4.7:  | Loop gain with the resonant controller                                                                                                           | 58 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 4.8:  | Insertion loss measurement setup                                                                                                                 | 58 |

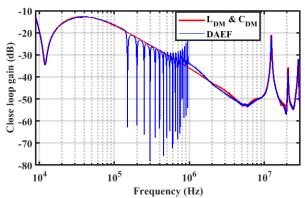

| Fig. 4.9:  | Insertion loss measurement of DAEF implementation                                                                                                | 59 |

| Fig. 4.10: | Experiment setup: (a) Equivalent circuit for experiment setup (b) Picture for experiment setup                                                   | 60 |

| Fig. 4.11: | Small-signal test of proposed DAEF under different noise source condition: (a) Test under $D = 0.5$ condition (b) Test under $D = 0.3$ condition | 61 |

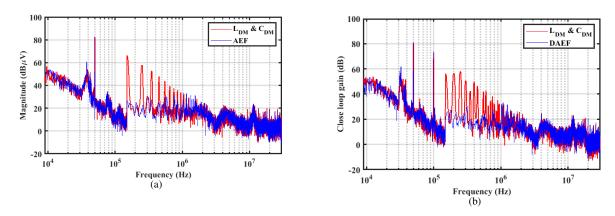

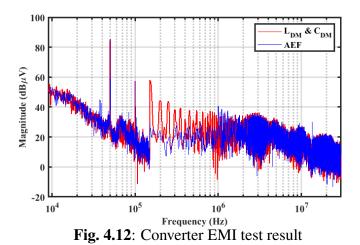

| Fig. 4.12: | Converter EMI test result                                                                                                                        | 61 |

# **List of Tables**

| TABLE 2.1: Design targets for 3 phase inverter                                  | 5  |

|---------------------------------------------------------------------------------|----|

| TABLE 2.2: Switching loss table for 3-L TNPC inverter                           | 6  |

| TABLE 2.3: Power semiconductors used in the evaluation                          | 7  |

| TABLE 2.4: Parameter used in the loss calculation                               | 8  |

| TABLE 2.5: Loss calculation for different topologies (single phase)             | 9  |

| TABLE 2.6: IEEE 1547 and IEEE 519 grid-tied inverter harmonics requirement      | 10 |

|                                                                                 |    |

| TABLE 3.1: Current dependent operation of the hybrid-switch-based inverter [12] | 22 |

| TABLE 3.2: CMV of space vectors                                                 | 26 |

| TABLE 3.3: Small vector's influence on NP potential                             | 27 |

| TABLE 3.4: Space Vector Choice and Alignment in Sector 3                        | 29 |

| TABLE 3.5: Space Vector Choice and Alignment in Sector 2                        | 29 |

| TABLE 3.6: Device Parameters                                                    | 31 |

#### **List of Publications**

1. H. Peng et al., "Practical Design and Evaluation of a High Efficiency 30-kVA Grid Connected PV Inverter with Hybrid Switch Structure", accepted for publication in 2020 IEEE Energy Conversion Congress and Exposition (ECCE)

Chapter 2 is made up of this paper

2. H. Peng et al., "Improved space vector modulation for neutral-point balancing control in hybrid-switch-based T-type neutral-point-clamped inverters with loss and common-mode voltage reduction," in CPSS Transactions on Power Electronics and Applications, vol. 4, no. 4, pp. 328-338, Dec. 2019.

doi: 10.24295/CPSSTPEA.2019.00031.

Chapter 3 is made up of this paper

3. H. Peng, B.Narayanasamy, Z.Yuan, A. Imran and F. Luo, "Selective Digital Active EMI filtering using Resonant Controller", submitted for review in *IEEE Transactions on Power Electronics*, **Under review**

Chapter 4 is made up of this paper

#### 1 Introduction

The power converter is heading towards higher power density, higher efficiency while having high reliability. Power converters are indispensable in automotive, aerospace, renewable energy applications as the motor drive inverter or grid-connected inverter. In data-centers and cloud infrastructure, rectifier and DC-DC converters are an essential part of the power supply. Within those applications, high power density, high efficiency, reliability are critical factors in the power architecture design.

Within the inverter topology, 3-L topology gradually draws attention from academia and industry (automotive, aerospace, renewable energy applications) due to its superior performance than the conventional two-level (2-L) topology. For the same device and configuration, 3-L topology provides higher efficiency, lower THD, and smaller passive filter size. Detailed system-level modeling and prototype building are available in the literature. The primary design issues for the 3-L inverter include but not limited to semiconductor selection, DC-link capacitor selection, output and input filter design, and hardware design.

Among wide bandgap (WBG) semiconductor devices, two materials suitable for power electronic applications are SiC MOSFET and GaN devices. However, the die size is still a bottleneck for WBG devices, which limited its application in high power applications. The benefits and challenges in paralleling WBG devices are available in the literature. The cost will increase dramatically if WBG devices are used in parallel. In order to overcome the higher cost, some literature proposes using the hybrid-switch structure. In the hybrid-switch structure, the principle is to parallel Si IGBT with SiC MOSFET for higher current rating applications to ensure low cost. However, the gate driver and the modulation strategy of such paralleling devices are complicated. Furthermore, in mixed switch combinations, the key idea for mixed switch combinations is to re-

place the Si IGBT with SiC MOSFET only in some switch positions within the topology, which enables the benefit of high efficiency, lower cost, and simple structure.

Furthermore, the combination of 3-L topology with mixed switch structure, features high efficiency, low cost, and simple structure. However, this structure has not been thoroughly investigated in 3 phase application yet. Within the 3 phase application, the main challenges will be system-level optimization and control and modulation. In this study, the system-level optimization is first introduced and follows the control and modulation of the proposed topology.

Lastly, when power electronics products are sold in the market, the converter or inverter itself needs to pass specific conducted emission standards. For solving electromagnetic interference (EMI) issues within the converter or inverter, EMI filter is introduced. Conventionally, the EMI filter occupies around 30 % of system volume while it becomes a bottleneck for the converter to gain higher power density. Thus, active EMI filter (AEF) are used for reducing the filter size. There are feedforward and feedback types of AEFs. For most of the offshore AEFs, the attenuation was limited 24 dB. In this study, a resonant controller-based voltage sensing current cancellation (VSCC) active EMI filter is pushing the attenuation 45 dB, which is 21 dB higher than the offshore AEFs.

This work is to solve the current issues within 3-L TNPC topology with hybrid-switch structure and active EMI filter. In Chapter 2, a system-level modeling, design, and testing of 3-L TNPC topology with hybrid switch structure is carried out. In Chapter 3, the modulation and control of 3-L TNPC topology with hybrid-switch structure is introduced. The active EMI filter is discussed, and resonant-controller based VSCC active EMI filter is introduced in Chapter 4. Finally, Chapter 5 gives the conclusion and future work.

# 2 Practical Design and Evaluation of a High Efficiency 30-kVA Grid Connected PV Inverter with Hybrid Switch Structure

Hongwu Peng, Zhao Yuan, Dereje Lemma Woldegiorgis, Asif Imran Emon, Balaji Narayanasamy, Yusi Liu, Fang Luo, Alan Mantooth,

#### Simon S. Ang, and Haider Ghazi Mhiesan

#### 2.1 Abstract

Photovoltaic (PV) grid-connected inverter exposes strong challenges to its efficiency, power density and reliability. This paper presents the design and test of a 30 kVA grid-connected inverter. The designed inverter achieved peak efficiency of 99.3% and a specific power of 2 kW/L by using a hybrid switch based three-level (3-L) T-type neutral point clamped (TNPC) topology. The hardware prototype presents excellent dynamic current and thermal distribution.

#### 2.2 Introduction

Photovoltaic sources are a promising and emission free renewable energy source [1], and grid connected inverters are one of the main units within the PV grid connected system. With the growth of wide bandgap (WBG) devices [2] such as SiC MOSFETs and GaN high-electron-mobility transistors (HEMT), grid-connected inverters realize benefits of smaller size, lower weight, and lower loss. Hybrid switch based converters [3–5] have merits of low conduction loss as well as low cost.

Two-level (2-L) inverters, 3-L neutral-point-clamped (NPC) inverters, and 3-L TNPC inverters are three typical inverter topologies for grid-connected application and will be compared in this paper. a 3-L TNPC with hybrid switch structure is then chosen for its superior performance

Fig. 2.1: A hybrid switch based TNPC structure[4]

under high switching frequency scenarios. A 3 phase TNPC with hybrid switch structure is then built and tested. Dynamic current sharing between devices [6] is ensured by adopting switching cell method. Continuous test is performed under full power rating for efficiency and thermal evaluation.

#### 2.3 System Level Design and Optimization

Fig. 2.2 shows the grid connected inverter which is to be designed. The design targets are shown in Table 2.1. There are 4 major elements in the inverter system, they are semiconductors (Si IGBTs or SiC MOSFETs), the DC-link capacitor, the output filter, and cooling components. In order to optimize the inverter system's performance, system level modeling need to be carried out in terms of the weight, cost, and loss of the main elements. However, the controller system, sensors, and gate drivers are ignored in the modeling part since they are similar for different designs. The design flowchart is shown in Fig. 2.3, which will be extensively discussed in this section.

**TABLE 2.1**: Design targets for 3 phase inverter

| Output power <i>Pout</i>                | 30 kVA        | DC-link voltage $V_{DC}$ | 800 V |

|-----------------------------------------|---------------|--------------------------|-------|

| Ouput line-to-line voltage $V_{LL,rms}$ | 460 V         | Grid frequency $f_0$     | 60 Hz |

| Power factor pf                         | 0.8 to 1      | Efficiency η             | 99%   |

| Switching frequency $f_{sw}$            | 70 <i>kHz</i> | Modulation techniques    | SPWM  |

Fig. 2.2: Three phase grid connected inverter

Fig. 2.3: Design methodology

#### 2.3.1 Inverter Topology and Semiconductor Stage Evaluation

In this section, four topologies are evaluated: 2-L 3 phase inverter using all-SiC MOSFET, 3-L 3 phase NPC inverter using SiC MOSFET and SiC schottky diode, 3-L 3 phase TNPC inverter using all-SiC MOSFET, and hybrid switch based 3-L 3 phase TNPC inverter. Schematic of those three topologies are shown in Fig. 2.4a to Fig. 2.4d, respectively.

[5] presented that for the high power factor application, clamping leg devices of the 3-L TNPC inverter will be mainly soft switching. For 3-L TNPC inverter, assuming the switching state 1, 0, and -1 represent the phase leg output being clamped to the input positive rail, the input middle point, and the input negative rail respectively. The switching loss table of 3-L TNPC can be given as Table 2.2. When the power factor target of the inverter is high enough, the switching loss of clamping leg is negligible. The hybrid switch based 3-L TNPC structure, which is shown in Fig. 2.4d, utilizes Si IGBT and SiC Schottky diode as clamping leg switches and SiC MOSFET for half-bridge switch positions. With SPWM, the clamping switches are soft-switching under the unity power factor, and thus, the utilization of Si IGBTs does not increase the switching loss. Therefore, the total semiconductor cost of this hybrid switch based 3-L TNPC is lower than that of the all-SiC 3-L TNPC inverter. While the cost is low, the efficiency is higher than that of the all-SiC 3-L TNPC inverter.

**TABLE 2.2**: Switching loss table for 3-L TNPC inverter

| Switching action                | 1 to 0 and 0 to 1                         | -1 to 0 and 0 to -1                       |  |

|---------------------------------|-------------------------------------------|-------------------------------------------|--|

| Switching loss $(I_{ph} > 0)$   | $E_{T1, off, on} = E_{Mos, off, on}$      | $E_{T2, on, off} = E_{Mos/IGBT, on, off}$ |  |

|                                 | $E_{T3, on, off} = 0$                     | $E_{T4, off, on} = 0$                     |  |

| Switching loss ( $I_{ph} < 0$ ) | $E_{T3, on, off} = E_{Mos/IGBT, on, off}$ | $E_{T4, off, on} = E_{Mos, off, on}$      |  |

|                                 | $E_{T1, off, on} = 0$                     | $E_{T2, on, off} = 0$                     |  |

To evaluate the performance of four topology candidates mentioned above, On company's semiconductor devices are chosen, detailed devices' parameters are shown in Table 3.6. Conduc-

**Fig. 2.4**: Evaluated converter topologies: (a) 2-L 3 phase inverter (b) 3-L 3 phase NPC inverter (c) 3-L 3 phase TNPC inverter (d) 3-L 3 phase TNPC inverter with hybrid switch structure

tion and switching characteristics of those devices can be extracted from the datasheet. To achieve target efficiency (99%) at rated power level (30 kw), 6 SiC MOSFETs, 3 SiC diodes, and 2 Si IGBTs are used in parallel for each switch position.

**TABLE 2.3**: Power semiconductors used in the evaluation

|                      | Voltage | Current | Typical switching loss                           | Cost p.u.(Mouser) |

|----------------------|---------|---------|--------------------------------------------------|-------------------|

| SiC MOSFET @ On-Semi | 1200 V  | 31 A    | $E_{on} = 258 \ \mu J, \ E_{off} = 52 \ \mu J$   | 7.64 \$           |

| NTHL080N120SC1       |         |         | $@800 V, 20 A, R_g = 4.7 \Omega$                 |                   |

| SiC Diode @ On-Semi  | 650 V   | 20 A    | $E_{sw} \approx 0$ (Very low                     | 5.91 \$           |

| FFSH2065A-D          |         |         | reverse recovery loss)                           |                   |

| Si IGBT @ On-Semi    | 650 V   | 40 A    | $E_{on} = 1390 \ \mu J, \ E_{off} = 541 \ \mu J$ | 2.51 \$           |

| FGH40T65SH           |         |         | $@400 V, 40 A, R_g = 6 Ω$                        |                   |

The power losses of semiconductor devices depend on the voltage/current waveforms and control methodologies. For simplicity, the SPWM modulation is utilized, and the output current waveform is assumed to be idealized sinusoidal function. Based on [6–8], the loss information of different topologies can be calculated as Table 2.5, the parameter which is used in the calculation is shown in Table 2.4.

The semiconductor stage efficiency for each topology is shown in Fig. 2.5. The cost of 2-L, 3-L NPC, 3-L TPC, and 3-L TNPC with hybrid switch combination are 275.04 \$, 656.46 \$, 550.08 \$, and 411.54 \$, respectively. 3-L NPC topology has lowest efficiency due to its largest conduction loss. At high switching frequency scenario, 2-L inverter's efficiency drops rapidly due to its high commutation voltage. For 70 kHz switching frequency application, 3-L TNPC has

**TABLE 2.4**: Parameter used in the loss calculation

| Parameter                                                                  | Definition                      |

|----------------------------------------------------------------------------|---------------------------------|

| $f_0$                                                                      | Grid frequency                  |

| w                                                                          | Grid angular frequency          |

| $P_{cond,MOS}$                                                             | Conduction loss of MOSFET       |

| $P_{cond,diode}$                                                           | Conduction loss of diode        |

| $P_{cond,IGBT}$                                                            | Conduction loss of IGBT         |

| $P_{sw,MOS}$                                                               | Switching loss of MOSFET        |

| $P_{sw,IGBT}$                                                              | Switching loss of IGBT          |

| φ                                                                          | Power dactor angle              |

| $I_{PK} = \frac{\sqrt{6}P_{out}}{3V_{LL,rms}}$                             | Peak phase current              |

| $i(k) = I_{pk} \cdot sin(\frac{k \cdot f_0}{f_{sw}} \cdot 2\pi - \varphi)$ | Transient current               |

| M × m                                                                      | Modulation index                |

| $R_{MOS,on}$                                                               | Conduction resistance of MOSFET |

| $V_{fw,diode}$                                                             | Forward voltage drop of diode   |

| $R_{diode}$                                                                | Conduction resistance of diode  |

| $V_{fw,IGBT}$                                                              | Forward voltage drop of IGBT    |

| $R_{IGBT}$                                                                 | Conduction resistance of IGBT   |

| $E_{MOS,on}(v,i)$                                                          | Switching on energy of MOSFET   |

| $E_{MOS,off}(v,i)$                                                         | Switching off energy of MOSFET  |

| $E_{IGBT,on}(v,i)$                                                         | Switching on energy of IGBT     |

| $E_{IGBT,off}(v,i)$                                                        | Switching off energy of IGBT    |

highest efficiency among all topologies. Morever, for the unity power factor scenario, efficiency of 3-L TNPC inverter with hybrid switch combination is comparable with that of all-SiC 3-L TNPC inverter. While the efficiency comparable, the cost of 3-L TNPC inverter with hybrid switch combination is much lower than that of all-SiC 3-L TNPC inverter. Thus, 3-L TNPC inverter with hybrid switch combination topology is chosen for semiconductor stage.

#### 2.3.2 LCL filter Design

The basic LCL structure can be found in Fig. 2.2.  $L_{inv}$ ,  $C_{out}$ , and  $L_{grid}$  donate the inverter side inductor, capacitor, and grid side inductor, respectively. The value selection of  $L_{inv}$  depends on the current ripple limitation of inverter output stage. The capacitor will add to the reactive power for the inverter system, normally the reactive power consumed by capacitor is limited to  $2 \sim 5\%$

**TABLE 2.5**: Loss calculation for different topologies (single phase)

| T 1          | C 1 4' 1                                                                                                                                                                                                                 |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Topology     | Conduction loss                                                                                                                                                                                                          |  |  |

| 2-L inverter | $P_{cond,MOS} = \frac{1}{\pi} \int_0^{\pi} i^2(k) R_{MOS,on} dwt (2.1)$                                                                                                                                                  |  |  |

| 3-L NPC      | $P_{cond,MOS} = \frac{1}{\pi} \int_0^{\pi} i^2(k) \cdot R_{MOS,on} \cdot (1 + i)$                                                                                                                                        |  |  |

| inverter     | $M \sin(wt) ) dwt 	(2.2)$                                                                                                                                                                                                |  |  |

|              | $P_{cond,diode} = \frac{1}{\pi} \int_0^{\pi} (1 - M sin(wt) ) \cdot$                                                                                                                                                     |  |  |

|              | $( i(k) V_{fw,diode} + i^2(k) \cdot R_{diode}) dwt$ (2.3)                                                                                                                                                                |  |  |

| 3-L TNPC     | $P_{cond} = \frac{1}{\pi} \int_0^{\pi} i^2(k) R_{MOS,on} \cdot (2 - i)$                                                                                                                                                  |  |  |

| inverter     | $M \sin(wt) ) dwt 	(2.4)$                                                                                                                                                                                                |  |  |

| 3-L TNPC     | $P_{cond,MOS} = \frac{1}{\pi} \int_0^{\pi} i^2(k) \cdot R_{MOS,on}$                                                                                                                                                      |  |  |

| inverter     | $M \sin(wt) ) dwt$ (2.5)                                                                                                                                                                                                 |  |  |

| with hybrid  | $P_{cond,diode} = \frac{1}{\pi} \int_0^{\pi} (1 - M sin(wt) ) \cdot$                                                                                                                                                     |  |  |

| switch       | $( i(k)  \cdot V_{fw,diode} + i^2(k) \cdot R_{diode}) dwt$ (2.6)                                                                                                                                                         |  |  |

| structure    | $P_{cond,IGBT} = \frac{1}{\pi} \int_0^{\pi} (1 - M sin(wt) ) \cdot$                                                                                                                                                      |  |  |

|              | $( i(k)  \cdot V_{fw,IGBT} + i^2(k) \cdot R_{IGBT}) \ dwt \ (2.7)$                                                                                                                                                       |  |  |

| Topology     | Switching loss                                                                                                                                                                                                           |  |  |

| 2-L inverter | $P_{sw,MOS} = 2f_0 \cdot \sum_{k=rac{0.f_{SW}}{2\pi \cdot f_0}}^{k=rac{\pi \cdot f_{SW}}{2\pi \cdot f_0}} (E_{MOS,on}(V_{DC}, i(k) )$                                                                                  |  |  |

|              | $+E_{MOS,off}(V_{DC}, i(k) ))$ (2.8)                                                                                                                                                                                     |  |  |

| 3-L NPC      | $+E_{MOS,off}(V_{DC}, i(k) )) \qquad (2.8)$ $P_{sw,MOS} = 2f_0 \cdot \sum_{k=\frac{0.f_{sw}}{2\pi \cdot f_0}}^{k=\frac{\pi \cdot f_{sw}}{2\pi \cdot f_0}} (E_{MOS,on}(\frac{V_{DC}}{2}, i(k) ) +$                        |  |  |

| inverter     | $E_{MOS,off}(\frac{\dot{V}_{DC}}{2}, i(k) )) \tag{2.9}$                                                                                                                                                                  |  |  |

| 3-L TNPC     | $P_{sw,MOS} = 2f_0 \cdot \sum_{k=\frac{0 \cdot f_{sw}}{2\pi \cdot f_0}}^{k=\frac{\pi \cdot f_{sw}}{2\pi \cdot f_0}} (E_{MOS,on}(\frac{V_{DC}}{2}, i(k) ) +$                                                              |  |  |

| inverter     | $E_{MOS,off}(\frac{V_{DC}}{2}, i(k) )) \tag{2.10}$                                                                                                                                                                       |  |  |

| 3-L TNPC     | $E_{MOS,off}(\frac{V_{DC}^{o}}{2}, i(k) )) \qquad (2.10)$ $P_{sw,MOS} = 2f_0 \cdot \sum_{k=\frac{\theta \cdot f_{SW}}{2\pi \cdot f_0}}^{k=\frac{\pi \cdot f_{SW}}{2\pi \cdot f_0}} (E_{MOS,on}(\frac{V_{DC}}{2}, i(k) )$ |  |  |

| inverter     | $+E_{MOS,off}(\underbrace{V_{DC}^{V_{DC}}}_{0.6\text{cm}}, i(k) )) \qquad (2.11)$                                                                                                                                        |  |  |

| with hybrid  | $+E_{MOS,off}(\frac{V_{DC}^{*}}{2^{o}, i(k) })) \qquad (2.11)$ $P_{sw,IGBT} = 2f_{0} \cdot \sum_{k=\frac{0.f_{sw}}{2\pi \cdot f_{0}}}^{k=\frac{0.f_{sw}}{2\pi \cdot f_{0}}} (E_{IGBT,on}(\frac{V_{DC}}{2}, i(k) )$       |  |  |

| switch       | $+E_{IGBT,off}(\frac{V_{DC}}{2}, i(k) )) \qquad (2.12)$                                                                                                                                                                  |  |  |

| structure    |                                                                                                                                                                                                                          |  |  |

of converter's power level. Then,  $L_{grid}$  need to be designed according to IEEE 1547 and IEEE 519 standard for harmonics of grid-tied inverter.

According to [9], the expression for calculating the minimum value for  $L_{inv}$  can be found in (2.13). Since the output sinusoidal peak current is around  $I_{PK} = 53.2A$ , the peak current ripple can be set to 40% of peak sinusoidal current. Thus, the calculated minimum inductance value for

Fig. 2.5: Semiconductor stage efficiency comparison

$L_{inv}$  is around 90 $\mu H$ , which will be used for physical design of the inductor. According to (2.13), the maximum capacitance value  $C_{out}$  is 7.5 $\mu H$  in order to limit the reactive power. Finally, 5 $\mu H$  MKP386M550125YT4 film capacitor from Vishay is chosen.

$$\Delta I_{max} \approx \frac{V_{DC} T_{sw}}{6 L_{inv}}, \ L_{inv} \approx 90 \mu H$$

(2.13)

$$Q_c \approx 3wV_{ph,rms}^2 C_{out} < 0.02 P_{out}, C_{out} < 7.5 \mu H$$

(2.14)

Based on the designed value of  $L_{inv}$  and  $C_{out}$ , the value of grid side inductor  $L_{grid}$  can be designed according to IEEE 1547 and IEEE 519 grid-tied inverter harmonics requirement. The IEEE 1547 and IEEE 519 grid-tied inverter harmonics requirement is shown in Table 2.6. The phase voltage is a PWM waveform. The filter need to attenuate phase voltage noise to obtain the output phase current waveform which meet the standard. The required attenuation can be expressed as (2.15).

TABLE 2.6: IEEE 1547 and IEEE 519 grid-tied inverter harmonics requirement

| Harmonic order                   | $< 11^{th}$ | $11 - 17^{th}$ | $17 - 23^{th}$ | $23 - 35^{th}$ | $> 35^{th}$ | THD  |

|----------------------------------|-------------|----------------|----------------|----------------|-------------|------|

| Limit (% of fundamental current) | < 4%        | < 2%           | < 1.5%         | < 0.6%         | < 0.3%      | < 5% |

$$G_{grid}(s) = \frac{I_{g,spec}(s)}{V_{inv,SPWM}(s)}$$

(2.15)

Morever, the attenuation (output current to input voltage) of LCL filter is expressed in (2.16). The attenuation spectrum of LCL filter need to be lower than the spectrum of required attenuation  $G_{grid}(s)$ . The LCL filter attenuation is plotted based on different value of  $L_{grid}$ , and the comparison between LCL filter attenuation and the required attenuation is shown in Fig. 2.6a. Since the switch frequency is as high as 70 kHz, the LCL filter attenuation is much lower than the grid code requirement in the high frequency range. For the low frequency range, which is shown in Fig. 2.6b, it can be observed that  $L_{grid}$  inductance need to be higher than 50  $\mu$ H. Finally,  $L_{grid} = 100 \ \mu$ H is chosen for the grid side inductor.

$$G_{LCL}(s) = \frac{I_g(s)}{V_{inv}(s)} = \frac{1}{L_{inv}L_{grid}C_{out}s^3 + (L_{inv} + L_{grid})s} < G_{grid}(s)$$

(2.16)

Fig. 2.6: LCL filter design in frequency domain: (a) attenuation of LCL filter comparing to required attenuation (b) zoom in of low frequency range

The final LCL filter value are:  $L_{inv} = 90 \ \mu H$ ,  $L_{grid} = 100 \ \mu H$ , and  $C_{out} = 5 \ \mu H$ . Normally the resonant frequency of the LCL filter  $f_{res}$  need to be higher than 10 times of the grid frequency,

and lower than half of the switching frequency. The resonance frequency  $f_{res}$  of the LCL filter is given by (2.17). Furthermore, the voltage drop on the filter inductor can be found in (2.18), which is much lower than the phase voltage. The LCL filter value design meets most of the design criteria mentioned in the reported literatures.

$$10f_0 < f_{res} = \frac{1}{2\pi} \sqrt{\frac{L_{inv} + L_{grid}}{L_{inv} L_{grid} C_{out}}} = 10.34 \text{ kHz} < 0.5 f_{sw}$$

(2.17)

$$V_{L,rms} = 2\pi f_0(L_{inv} + (L_{grid}) \cdot I_{rms} \approx 2.7 \text{ V} << V_{ph,rms} = 265.6 \text{ V}$$

(2.18)

The area product  $A_p$  design method, which is expressed in (2.19), is used for inductor design.  $K_0$  is the filling factor for the inductor window area, which is normally set at 0.3 to 0.4 with insulation and support consideration. J is the winding current density, which is normally set as  $3.5 \, A/mm^2$  under natural air cooling conditions. To further reduce the skin effect in high switching frequency application, Litz wire (22 AWG with 45 strand, 6 AWG-equivalent) is selected for inductor winding.  $B_m$  is the maximum flux density in the inductor core, which is chosen based on core material specification.  $A_e$  and  $A_w$  donates the inductor's core cross sectional area and window area, respectively. Magnetic powder core [10] is selected for core design. For inverter side inductor  $L_{inv}$ , MPP 60  $\mu$  core with 62 cm outer diameter is chosen, and 22 turns of windings are implemented. For the grid side inductor  $L_{grid}$ , high flux 125  $\mu$  core with 62 cm outer diameter is chosen, and 18 turns of windings are implemented.

$$A_p = A_e A_w > \frac{LI_{rms}I_{max}}{K_0 JB_m} \tag{2.19}$$

#### 2.3.3 DC-link capacitor

The DC-link capacitor volume occupies a large portion of the inverter system's volume. In this study, 3 major factors are taken into consideration for the DC-link capacitor selection: DC-link voltage ripple, neutral point voltage ripple, and capacitor's current rating.

For 3-L inverter, assuming two capacitors  $C_1$  and  $C_2$  are in parallel to provide neutral point. The total DC-link capacitance is given by  $C_{DC-link} = 0.5C_1 = 0.5C_2$ . [8] showed that the ripple voltage on the DC-link can be obtained by (2.20). The required DC-link capacitor  $C_{DC-link}$  to keep the DC-link voltage ripple  $\Delta V_{dc}$  within 0.5% of total DC-link voltage  $V_{dc}$  can be obtained as 24.3  $\mu F$ , and then  $C_1 = C_2 = 48.6 \mu F$ .

$$\Delta V_{dc} = \frac{V_{ph,rms}I_{ph,rms}}{2\pi f_{sw}V_{DC}C_{DC-link}} (\sqrt{3} - \frac{\pi}{3}) < 0.5\%V_{dc}$$

(2.20)

However, for 3-L inverter, the neutral point voltage  $V_{np}$  will also have variation due to the neutral point current. In order to limit the neutral point voltage variation, neutral point balancing (NPB) control need to be implemented. [11] proposed a NPB control strategy using zero sequence injection. Furthermore, [12] gave the analytical relationship between neutral point voltage variation  $\Delta V_{np}$  and the circuit parameters under the zero sequence injection NPB control frame, and the expression is given by (2.21).  $C_{np}$  is the total neutral point capacitance, which satisfies  $C_{np} = 2C_1 = 2C_2$ .  $k(M, cos(\varphi))$  is a parameter associate with worst case power factor and modulation index. For the system parameters in the paper  $(cos(\varphi) = 0.8 - 1 \text{ and } M \approx 0.94)$ ,  $k(M, cos(\varphi))$  is approximately 0.1. To limit the neutral point voltage ripple  $\Delta V_{np}$  to be within 2% of the DC-link voltage  $V_{DC}$ , the neutral point capacitance  $C_{np}$  can be calculated as  $C_{np} = 651\mu F$ . To leave some design margin,  $C_{np}$  is finally designed as  $C_{np} = 840\mu F$ , and then  $C_1 = C_2 = 420\mu F$ .

$$\Delta V_{np} = \frac{V_{DC}I_{LL,rms}}{2C_{np}wV_{LL,rms}} \cdot k(M,cos(\varphi)) < 2\%V_{DC}$$

(2.21)

The DC-link capacitor suffers both fundamental frequency harmonics current and switching frequency harmonics current. [13] gave the expression of DC-link capacitor's current, which can be found in (2.22)-(2.24). With the system parameter discussed in the paper, the RMS current of the DC-link capacitor  $I_{cap,rms}$  can be calculated as 19 A.

$$I_{avg} = \frac{3}{4} I_{PK} M cos(\varphi) \tag{2.22}$$

$$I_{rms} = \sqrt{\frac{3I_{PK}^2 M(\sqrt{3} + \frac{2}{\sqrt{3}}cos(2\varphi))}{4\pi}}$$

(2.23)

$$I_{cap,rms} = \sqrt{I_{rms}^2 - I_{avg}^2} \tag{2.24}$$

In summary, the final DC-link capacitor  $C_{DC-link}$  is set to be  $210\mu F$ , which is composed of two capacitor  $C_1 = C_2 = 420\mu F$  in parallel. For each of the  $C_1$  and  $C_2$ , 14 of 30  $\mu F$ , 800 V DCP4L053007HD2KSSD film capacitors from WIMA are chosen.

#### 2.4 Hardware Development and Experiment

The final architecture is shown in Fig. 2.7a, on  $T_1$  and  $T_4$  there are six SiC MOSFETs in parallel. And for  $T_2$  and  $T_3$  position, there are two IGBTs in parallel. For  $D_2$  and  $D_3$  position, there are three SiC Schottky diodes in parallel. The exact position of devices on hardware is shown in Fig. 2.7b. Entire 3-phase 3-L inverter prototype with heatsink is shown in Fig. 2.7c.

**Fig. 2.7**: Hardware prototype for 3 phase 3-L inverter with hybrid switch structure: (a) Structure of 3-L TNPC phase leg (b) Top view of prototype (c) 3-phase 3-L TNPC inverter

First, the double pulse test (DPT) for evaluating the current sharing and switching performance is conducted under 800 V DC voltage, 60A load current condition. DPT result for  $T_4$  is shown Fig. 2.9, where dynamic current sharing is excellent for both turn on and turn off transient.

**Fig. 2.8**: DPT test waveform for  $T_4$  device: (a) Turn on transient of  $T_4$  position (b) Turn off transient of  $T_4$  position

A 3-phase test is conducted under a full power rating (30 kVA) in laboratory. The DC-link voltage is set at 800 V. The fundamental frequency is set to 2 kHz and the power factor (pf) under test is 0.3 due to the equipment limitation. The switching frequency is set to 70 kHz. The test setup is shown in Fig. 2.9a, and the line-to-line voltage, phase current waveform is shown in Fig. 2.9b.

**Fig. 2.9**: Continuous test for 3 phase 3-L TNPC prototype: (a) Test setup for 3 phase testing (b) Testing waveform

Fig. 2.10: Resistive load testing setup

The power testing of the inverter is also conducted under 30 kW resistive load. The basic test setup is shown in Fig. 2.10. And the schematic can be find in Fig. 2.11a. The testing waveform for the inverter under rated voltage and power is shown in Fig. 2.11b. As it can be seen from the figure, the input voltage is set to be 800 V, and the output line-line voltage is 460 V, while the output current is set to be 52 A.

The thermal information is also captured during the testing after 20 minutes burning. As it's shown in the Fig. 2.12b, the higher temperature of the entire prototype is only around 40 degree C, which might be due to the inaccuracy of the thermal camera. Taking inaccuracy of the thermal

Fig. 2.11: Resistive load testing: (a) Resistive load testing schematic (b) Resistive load testing waveform

camera into account, the converter is still running at a safe temperature range (case temperature lower than 80 degree C). The thermal image result validate that the thermal design of the prototype has enough margin, which can ensure the inverter will still be safe operating even under heavy load.

The efficiency of the entire inverter system is also measured from the test setup, which is shown in Fig. 2.13a. The input and output power are both obtained from oscilloscope and Yokogawa WT1600 power analyzer. After comparison of both data, an accurate efficiency curve is drawn in Fig. 2.13b. As it can be seen from the figure, the highest efficiency of the inverter is around 99.26 %. At rated power (30 kW), the efficiency of the entire inverter is around 99.07 %.

#### 2.5 Conclusion

Based on efficiency, cost, and weight comparison for different topology options, a 3-phase 3-L TNPC with hybrid switch combination is selected. The hardware prototype is then built and test. DPT shows good current sharing performance between paralleled devices. Three-phase test-

Fig. 2.12: Thermal image of the resistive load test: (a) original test setup (b) thermal image

**Fig. 2.13**: Efficiency measurement of the inverter: (a) Efficiency measurement setup (b) Efficiency measured

ing under full power rating is carried out. The thermal measurement as well as the efficiency measurement are conducted, which validate the inverter system design.

#### 2.6 Bibliography

- [1] W. Li, Y. Gu, H. Luo, W. Cui, X. He, and C. Xia, "Topology review and derivation methodology of single-phase transformerless photovoltaic inverters for leakage current suppression," *IEEE Transactions on Industrial Electronics*, vol. 62, no. 7, pp. 4537–4551, 2015.

- [2] C. Chen, Y. Chen, Y. Tan, J. Fang, F. Luo, and Y. Kang, "On the practical design of a high power density sic single-phase uninterrupted power supply system," *IEEE Transactions on Industrial Informatics*, vol. 13, no. 5, pp. 2704–2716, 2017.

- [3] A. Deshpande and F. Luo, "Design of a silicon-wbg hybrid switch," in *Wide Bandgap Power Devices and Applications (WiPDA), 2015 IEEE 3rd Workshop on.* IEEE, 2015, pp. 296–299.

- [4] A. Anthon, Z. Zhang, M. A. Andersen, D. G. Holmes, B. McGrath, and C. A. Teixeira, "The benefits of sic mosfet s in a t-type inverter for grid-tie applications," *IEEE Transactions on Power Electronics*, vol. 32, no. 4, pp. 2808–2821, 2017.

- [5] H. Peng, Z. Yuan, X. Zhao, B. Narayanasamy, A. Deshpande, A. I. Emon, F. Luo, and C. Chen, "Improved space vector modulation for neutral-point balancing control in hybridswitch-based t-type neutral-point-clamped inverters with loss and common-mode voltage reduction," CPSS Transactions on Power Electronics and Applications, vol. 4, no. 4, pp. 328– 338, 2019.

- [6] Z. Yuan, H. Peng, A. Deshpande, B. Narayanasamy, A. I. Emon, F. Luo, and C. Chen, "Design and evaluation of laminated busbar for 3-level t-type npc power electronics building block with enhanced dynamic current sharing," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, 2019.

- [7] D. Graovac, M. Purschel, and A. Kiep, "Mosfet power losses calculation using the data-sheet parameters," *Infineon application note*, vol. 1, pp. 1–23, 2006.

- [8] A. Nawawi, C. F. Tong, S. Yin, A. Sakanova, Y. Liu, Y. Liu, M. Kai, K. Y. See, K.-J. Tseng, R. Simanjorang *et al.*, "Design and demonstration of high power density inverter for aircraft applications," *IEEE Transactions on Industry Applications*, vol. 53, no. 2, pp. 1168–1176, 2016.

- [9] Y. Jiao, "High power high frequency 3-level neutral point clamped power conversion system," Ph.D. dissertation, Virginia Polytechnic Institute and State University, 2015.

- [10] 2017 Magnetics Powder Core Catalog, Magnetics, 2017.

- [11] S. Ogasawara, T. Sawada, and H. Akagi, "Analysis of the neutral point potential variation of neutral-point-clamped voltage source pwm inverters," *IEEJ Transactions on Industry Applications*, vol. 113, no. 1, pp. 41–48, 1993.

- [12] J.-i. Itoh and T. Tanaka, "Minimum neutral clamp capacitor design considering voltage satu-

- ration for a three-level inverter," in 8th International Conference on Power Electronics-ECCE Asia. IEEE, 2011, pp. 1411–1418.

- [13] K. Gopalakrishnan, S. Das, and G. Narayanan, "Analytical expression for rms dc link capacitor current in a three-level inverter," in *Proc. Conf. Centenary*, 2011.

# 3 Space Vector Modulation for Neutral-Point Balancing Control in Hybrid -Switch-Based T-type Neutral-Point-Clamped Inverters With Loss and Common-Mode Voltage Reduction

Hongwu Peng, Zhao Yuan, Xingchen Zhao, Balaji Narayanasamy, Amol Deshpande, Asif Imran Emon, Fang Luo, and Cai Chen

#### 3.1 Abstract

This paper compares different space vector modulation (SVM) strategies for neutral-point voltage balancing (NPVB) control in three-level (3-L) T-type neutral-point-clamped (TNPC) inverters, and proposes an improved SVM trimmed for NPVB control in hybrid-switch-based 3-L TNPC inverter with the features of loss and common-mode voltage (CMV) reduction. The proposed SVM strategy uses a new principle of small vector selection and vector sequence, and thus, it can balance the neutral point (NP) potential and achieve soft-switching of clamping leg simultaneously. The paper includes detailed analysis for circuit commutation mode, loss breakdown, and common-mode voltage patterns under different operation conditions. The circuit simulations and experiments are carried out in the last part of this paper to validate the proposed SVM strategy.

#### 3.2 Introduction

Three-level T-type neutral-point-clamped (3-L TNPC) inverter has higher efficiency and lower total harmonic distortion (THD) compared to two-level inverter, and it has become popular in high-speed motor drives and all-electric aircraft applications[1–5]. Emerging silicon carbide (SiC) MOSFET has lower losses and high switching speed compared to Si IGBT and enables higher efficiency and power density in power converters[6–11]. SiC MOSFET is becoming a

major competitor and replacement for Si IGBT in power electronics systems.

High-current rated Si IGBT Low-current rated SiC MOSFET

Fig. 3.1: Structure of the hybrid switch

**TABLE 3.1**: Current dependent operation of the hybrid-switch-based inverter [12]

| Conditions: | SiC MOSFET voltage drop is   | Load current is within  | Load current exceed    |

|-------------|------------------------------|-------------------------|------------------------|

|             | lower than Si IGBT threshold | SOA of SiC MOSFET       | SOA of SiC MOSFET      |

| Operations: | Only SiC MOSFET is turned on | Hybrid switch operation | Only IGBT is turned on |

**Fig. 3.2**: T-type inverter with hybrid switch structure 1 [13]

However, the state-of-the-art die size limit and the high cost of SiC MOSFET are the bottlenecks for its high-current commercial applications. Therefore, [13] proposed a hybrid switch concept, as shown in Fig. 3.1. By adjusting the switching sequence of the two switches, the T-type inverter with the hybrid switch (hybrid structure 1) [14–16], which is shown in Fig. 3.2, can have low switching loss from SiC MOSFET switching, and low conduction loss from IGBT conduction. However, due to the long discharging time of the carriers inside the IGBT, the Si-SiC hybrid switch operation mode have a minimum duty cycle limitation [17], which deteriorates the output

total harmonic distortion performance. Furthermore, the hybrid-switch-based 3-L TNPC increases the system complexity in terms of the gate driver and power loop design [18–20]. Because of more paralleled semiconductors, more gate drivers and more gating signals are required. [12] mentioned that the Si-SiC hybrid switch structure should ensure the safe operation area (SOA) of the SiC MOSFET. Table 3.1 illustrates the current dependent operation in [12].

Fig. 3.3: T-type inverter with hybrid switch structure 2 [21]

To reduce the system complexity as well as improve the output THD performance,  $M_1$ ,  $M_4$ ,  $Q_2$ ,  $Q_3$ ,  $D_2$  and  $D_3$  in hybrid structure 1 are selected to operate, and the new structure is shown in Fig. 3.3 [21]. The hybrid structure 2 utilizes Si IGBT and SiC Schottky diode as clamping leg switches and SiC MOSFET for half-bridge switch positions. With SPWM, the clamping switches are soft-switching under the unity power factor, and thus, the utilization of Si IGBTs does not increase the switching loss. Therefore, the total semiconductor cost of this hybrid switch combination 3-L TNPC is lower than that of the all-SiC 3-L TNPC inverter. While the cost is low, the efficiency is higher than that of the all-SiC 3-L TNPC inverter.

Although hybrid structure 2 possesses the merits of low complexity and high efficiency, it has not been fully validated in the 3-phase 3-L TNPC system yet. One of the main challenges is to design a proper space vector modulation (SVM) scheme, which needs to consider the soft switching feature of the clamping leg, neutral point balancing (NPB) [22–25], and the common-

mode voltage (CMV) performance. This paper provides a criterion to choose the appropriate SVM for T-type inverter with hybrid structure 2 under different conditions. Firstly, this paper obtains the switching energy of T-type inverter with hybrid structure 2 by experimental double pulse test (DPT) result, then 3 different SVM schemes are discussed in terms of switching loss, NPB, and output CMV voltage performance.

The organization of the paper is as follows. Section II summarizes the soft-switching conditions for 3-L TNPC with hybrid structure 2, then loss analysis, neutral point balancing capability and common-mode noise voltage comparison of 3 different SVM schemes are discussed. In Section III, a 20 kVA hardware is built, the DPT is firstly performed to obtain exact switching loss, followed by the analysis and comparison of semiconductor loss breakdown, EMI spectrum, and neutral point voltage ripple for three SVMs. Section IV presents the conclusion of the preferred modulation scheme.

#### 3.3 Analysis of Different Modulation on Hybrid Switch Based 3-Phase 3-L TNPC

For switching loss reduction [21] and NPB [22–25] in 3 phase 3-L TNPC inverter with hybrid switch combination, SVM 1 with NPB [23], SVM 2 with NPB [24], and improved SVM 2 with NPB are compared, and 1<sub>st</sub> sector of the space vector modulation hexagon is given as an example. The nearest three space vector (NTSV) [26] and discontinuous pulse width modulation (DPWM) [27] are adopted to track the reference vector and further reduce the switching loss.

In this chapter, switching loss and soft-switching condition of clamping leg is discussed first in 3-L TNPC with the hybrid switch combination. Then three different SVM schemes are compared in terms of switching losses, neutral point balancing capability, and CMV performance, which gives guidance for hardware design and PWM modulation choice.

**Fig. 3.4**: Different switching transitions when the phase output is positive or neutral: (a) Switch transition 1 (Positive phase current) (b) Switch transition 2 (Positive phase current) (c) Switch transition 3 (Negative phase current) (d) Switch transition 4 (Negative phase current)

### 3.3.1 Preferred Switch Pairs in Terms of Switching Loss Reduction

Since switching loss of Si IGBT is much higher than SiC MOSFET, hard switching of Si IGBT on clamping leg in 3-L TNPC inverter with hybrid switch combination should be avoided or minimized. As shown in Fig. 3.4(a), when the phase current is positive, and the phase output voltage is transitioning from positive to neutral,  $T_1$  is hard switching off, and then  $T_2$  and  $D_3$  are soft switched on. From Fig. 3.4(b) we can know that when phase current is positive, and the phase output voltage is transiting from neutral to positive, clamping leg devices are soft switched off,

**TABLE 3.2**: CMV of space vectors

| Space vector | $V_1$        | $V_2$        | $V_3$       | $V_4$       |

|--------------|--------------|--------------|-------------|-------------|

| CMV          | $-1/3V_{dc}$ | $-1/6V_{dc}$ | 0           | $1/6V_{dc}$ |

| Space vector | $V_5$        | $V_6$        | $V_7$       | $V_8$       |

| CMV          | $1/3V_{dc}$  | $-1/6V_{dc}$ | $1/6V_{dc}$ | 0           |

and  $T_1$  is hard switched on. Moreover, when the phase current is negative, and phase output is transitioning from positive to neutral or from neutral to positive,  $T_3$  is hard switched on and hard switched off.

In summary, when phase current is positive, switch pair 1 and 0 is preferred since the clamping leg is soft-switching, as shown in Fig. 3.4(a) and Fig. 3.4(b). Switch pair 0 and -1 should be avoided since clamping leg switch  $T_2$  is hard switching. Symmetrically when phase current is negative, switch pair 0 and -1 is preferred to obtain the soft-switching character of clamping leg, and switch pair 1 and 0 should be avoided or minimized to reduce the switching loss of Si IGBT, as shown in Fig. 3.4(c) and Fig. 3.4(d). Based on the aforementioned analysis, different SVMs can be compared in terms of switching loss, more detailed information will be given in the later section.

### 3.3.2 Common Mode Voltage of 3L TNPC Inverter

Assuming that only heatsink is grounded, the equivalent model of 3 phase 3-L TNPC [28–33] is drawn in Fig. 3.5, with the consideration of all the semiconductor's junction to heatsink and output to ground capacitance. Also, a simplified model is given in Fig. 3.6, which indicates that the CMV noise can be modeled through (3.1).

$$V_{CM} = (V_{AN} + V_{BN} + V_{CN})/3 (3.1)$$

Fig. 3.5: Three-phase 3-L TNPC model with the parasitic capacitor

Fig. 3.6: Three-phase 3-L TNPC CMV path

Space vectors in sector 1 of the modulation hexagon, which are shown in Fig. 3.7, are given as an example for CMV calculation. As shown in Table 3.2, small vector  $V_1$  and  $V_5$  have the largest CMV, while zero vector  $V_8$  and medium vector  $V_3$  do not contribute to CMV.

### 3.3.3 Switching Loss Reduction, NPB, and CM Voltage Analysis for Different SVM Schemes

Firstly, space vectors of sector 1 are marked out in Fig. 3.7 and small vectors' influence on neutral point potential are stated in Table 3.3. For simplicity, the region 3 and 2 are analyzed and compared for three kinds of SVM schemes, choices of small vectors and alignment in the region 1 and 4 are similar to the region 3 and 2. From Table 3.2 it is known that small vectors  $V_2$  and  $V_4$

**TABLE 3.3**: Small vector's influence on NP potential

| Small Vector Angle | Discharge NP     | Charge NP |

|--------------------|------------------|-----------|

| $0^o$              | $\overline{V_4}$ | $V_1$     |

| 60°                | $V_5$            | $V_2$     |

have lower CM voltage than  $V_1$  and  $V_5$ . Less small vectors like  $V_2$  and  $V_4$  are chosen, smaller CM voltage the SVM schemes can get.

Fig. 3.7: Three-phase three-level space vector hexagon

# The region 3 of Sector 1

The space vector choice and alignment for SVM 1, SVM 2, and improved SVM 2 are shown in Table 3.4. For SVM 1 scheme, both of the small vectors  $V_1$ ,  $V_2$ ,  $V_4$ , and  $V_5$  are used for balancing the neutral point potential, and B phase switching state changes between 1 and 0 plus 0 and -1. Since SVM 1 does not consider the B phase current direction, B phase has hard switching operations on the clamping leg. For SVM 2 scheme, the region 3 is divided into the region 3.1 and the region 3.2 according to B phase voltage polarity. In the region 3.1, only  $V_1$  and  $V_4$  small vectors are used for balancing the neutral point potential. In the region 3.2, only  $V_2$  and  $V_5$  small vectors are used for balancing the neutral point potential. B phase clamping leg is always soft-switching under unity PF. Improved SVM 2 scheme is proposed to reduce the switching loss under the wider power factor range. When the B phase current is negative,  $V_1$  and  $V_4$  small vectors are used for balancing the neutral point potential.  $V_2$  and  $V_5$  small vectors are used when the B phase current is

**TABLE 3.4**: Space Vector Choice and Alignment in Sector 3

| The region 3 of Sector 1   | Discharge NP                                                                   | Charge NP                                                                                                             |

|----------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| SVM 1                      | $V_3$ - $V_2$ - $V_1$ - $V_2$ - $V_3$                                          | <i>V</i> <sub>3</sub> - <i>V</i> <sub>4</sub> - <i>V</i> <sub>5</sub> - <i>V</i> <sub>4</sub> - <i>V</i> <sub>3</sub> |

| SVM 2 & 0°-30°             | $V_1$ - $V_2$ - $V_3$ - $V_2$ - $V_1$                                          | V <sub>2</sub> -V <sub>3</sub> -V <sub>4</sub> -V <sub>3</sub> -V <sub>2</sub>                                        |

| SVM 2 & 30°-60°            | $V_4$ - $V_3$ - $V_2$ - $V_3$ - $V_4$                                          | V <sub>5</sub> -V <sub>4</sub> -V <sub>3</sub> -V <sub>4</sub> -V <sub>5</sub>                                        |

| Improved SVM 2 & $I_b < 0$ | $V_1$ - $V_2$ - $V_3$ - $V_2$ - $V_1$                                          | V <sub>2</sub> -V <sub>3</sub> -V <sub>4</sub> -V <sub>3</sub> -V <sub>2</sub>                                        |

| Improved SVM 2 & $I_b > 0$ | V <sub>4</sub> -V <sub>3</sub> -V <sub>2</sub> -V <sub>3</sub> -V <sub>4</sub> | V <sub>5</sub> -V <sub>4</sub> -V <sub>3</sub> -V <sub>4</sub> -V <sub>5</sub>                                        |

**TABLE 3.5**: Space Vector Choice and Alignment in Sector 2

| The region 2 of Sector 1 | Discharge NP                          | Charge NP                                                                      |

|--------------------------|---------------------------------------|--------------------------------------------------------------------------------|

| SVM 1                    | $V_1$ - $V_6$ - $V_3$ - $V_6$ - $V_1$ | V <sub>6</sub> -V <sub>3</sub> -V <sub>4</sub> -V <sub>3</sub> -V <sub>6</sub> |

| SVM 2                    | $V_1$ - $V_6$ - $V_3$ - $V_6$ - $V_1$ | V <sub>6</sub> -V <sub>3</sub> -V <sub>4</sub> -V <sub>3</sub> -V <sub>6</sub> |

| Improved SVM 2           | $V_1$ - $V_6$ - $V_3$ - $V_6$ - $V_1$ | V <sub>6</sub> -V <sub>3</sub> -V <sub>4</sub> -V <sub>3</sub> -V <sub>6</sub> |

positive. Improved SVM 2 scheme is basically the same as SVM 2 scheme under the unity power factor, and since it considers the phase current direction for choosing the small vector, and thus, it has lower losses on clamping leg under the non-unity power factor case.

### The region 2 of Sector 1

For region 2, modulation strategies of SVM 1, SVM 2, and improved SVM 2 are the same, which are shown in Table 3.5.  $V_1$  and  $V_4$  are chosen to discharge and charge the neutral point voltage, and alignments are  $V_6$ - $V_3$ - $V_4$ - $V_3$ - $V_6$  and  $V_1$ - $V_6$ - $V_3$ - $V_6$ - $V_1$  when the neutral point voltage is lower and higher than half of the DC-link voltage. Soft switching can be achieved on the clamping leg of B phase under the unity power factor.

### **Summary of Different SVM Schemes**

In general, the improved SVM 2 scheme has the lowest switching loss on clamping leg.

Moreover, under the non-unity power factor condition, SVM 1 has better neutral point balancing

Fig. 3.8: Switching loss information for SiC MOSFET position and Si IGBT position

ability than SVM 2 and improved SVM 2. According to Table 3.2, V1 and V5 have the highest CM voltage. Since SVM 2 and improved SVM 2 exclude  $V_1$  or  $V_5$  for reducing the switching loss, and SVM 1 employs both of the  $V_1$  and  $V_5$  for NPB, SVM 2 and improved SVM 2 have relatively lower CMV than that of SVM 1.

## 3.4 Experimental Test and Loss Breakdown

A 6 kVA 3-phase 3-L TNPC prototype is built to evaluate the efficiency and CM voltage noise spectrum with different SVM, upper and lower DC-link capacitors are 150  $\mu$ F each. As shown in Table 3.6, we have chosen 1200 V/30 A SiC MOSFET, C3M0075120K from Wolfspeed, and 600 V/30 A Si-IGBT IKZ50N65EH5 from ROHM, and FFSH1665A SiC Schottky diode, for experiment validation. Top leg and bottom leg switches are rated for 1.2 kV, and DC-link voltage is set to be 800 V to remain some safety margin. Output RMS voltage is set to 208 V to meet one of the grid standards. Switching frequency is set to be 70 kHz to reduce the passive components' volume. The prototype is composed of three 2-kVA single-phase 3-L TNPC, as shown in Fig.3.9.

Fig. 3.9: Test setup of DPT

**TABLE 3.6**: Device Parameters

|                                              | Voltage (V) | Current (A) |

|----------------------------------------------|-------------|-------------|

| SiC MOSFET (Wolfspeed-C3M0075120K)           | 1200        | 30          |

| Si IGBT<br>(ROHM-RGCL60TS60D)                | 600         | 30          |

| SiC Shottky diode<br>(Wolfspeed-C3M0075120K) | 650         | 23          |

## **Switching Energy Evaluation of the Three-Level Inverter**

Switching energy calculation based on the devices' voltage and devices' current waveform is comprehensively evaluated in [34–36]. DPT is firstly performed to obtain the switching transitions of both SiC MOSFET and IGBT devices. As mentioned in [37], switching energy in 3-L phase leg is different from 2L half-bridge due to the device's junction capacitance, so the double pulse test in this paper is performed based on the single-phase 3-L TNPC platform. In this way, loss analysis using switching energy data from the double pulse test on the 3-L TNPC platform gives more accurate results. The accurate switching energy information for SiC MOSFETs and Si IGBT switch is shown in Fig. 3.8.

**Fig. 3.10**: Loss breakdown of semiconductor devices at different power factors: (a) Loss breakdown when PF=1 (b) Loss breakdown when PF=0.9 (c) Loss breakdown when PF=0.8 (d) Loss breakdown when PF=0.7

#### Semiconductor Loss Breakdown and EMI Performance Evaluation

Switching energy from DPT and device conduction performance in the component datasheet are used, and a detailed semiconductor loss breakdown can be obtained in simulation. While the total power level is 6 kVA, and the switching frequency is 70 kHz.

For the near unity PF case, the loss breakdown for different modulation schemes is listed in Fig. 3.10(a), and total semiconductor loss using SVM 1, SVM 2, and improved SVM 2 are respectively 17.1 W, 16 W, and 16 W. As shown in the diagram, under the unity power factor case,

total loss of the SVM 2 and the improved SVM 2 are 6.4% lower than using SVM 1. All of the SVMs have the same neutral point voltage ripple, which is around 2 V due to the hysteresis control algorithm at half of the switching frequency and switching actions at switching frequency.